## Digital Logic Gates :

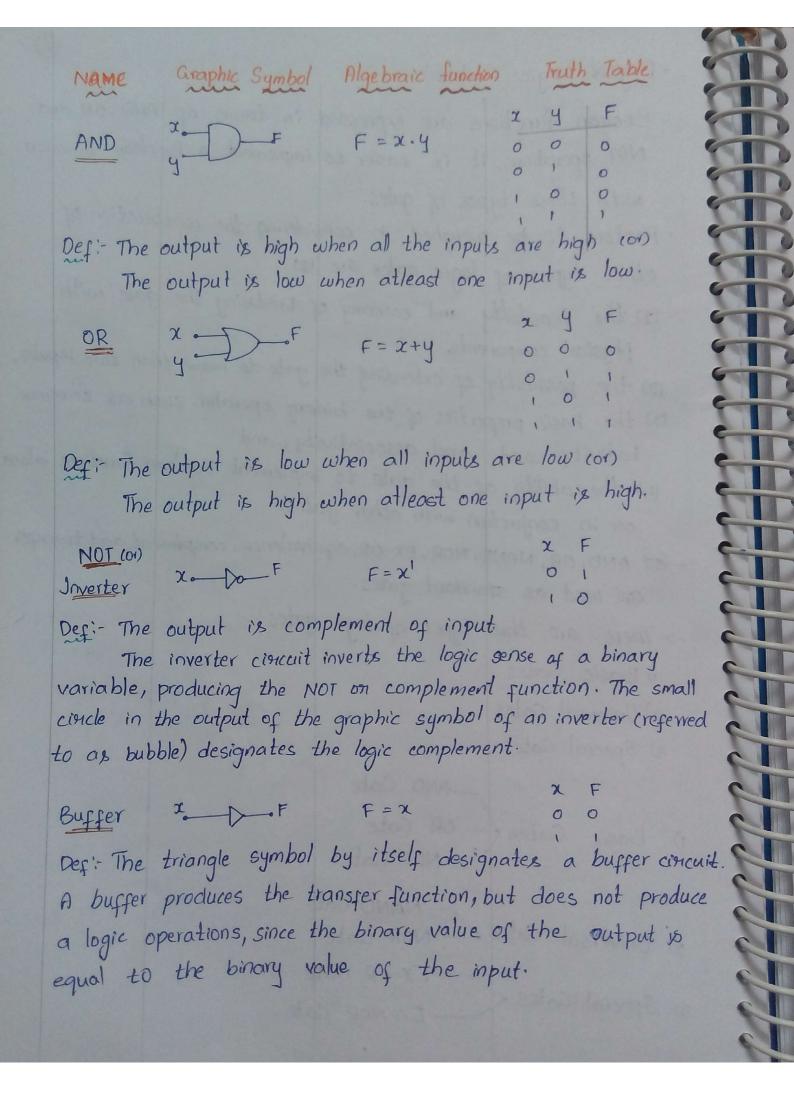

- Boolean functions are expressed in terms of AND, OR and NOT operations, it is easier to implement a Boolean function with these types of gates.

Factors to be weighed in considering the construction of

other types of logic gates are

(1) the feasibility and economy of producing the gate with

12) the possibility of extending the gate to mome than two inputs,

(3) the basic properties of the binary operator, such as commutativity and and associativity, and

(4) the ability of the gate to implement Boolean functions alon

on in conjuction with other gates.

(6) AND, OR, NAND, NOR, Ex-OR, equivalence, complement and transfer are used as standard gates.

- -> There are three types of logic gates

- i) Basic Gates

- 2) Universal Gates

- 3) Special Gates.

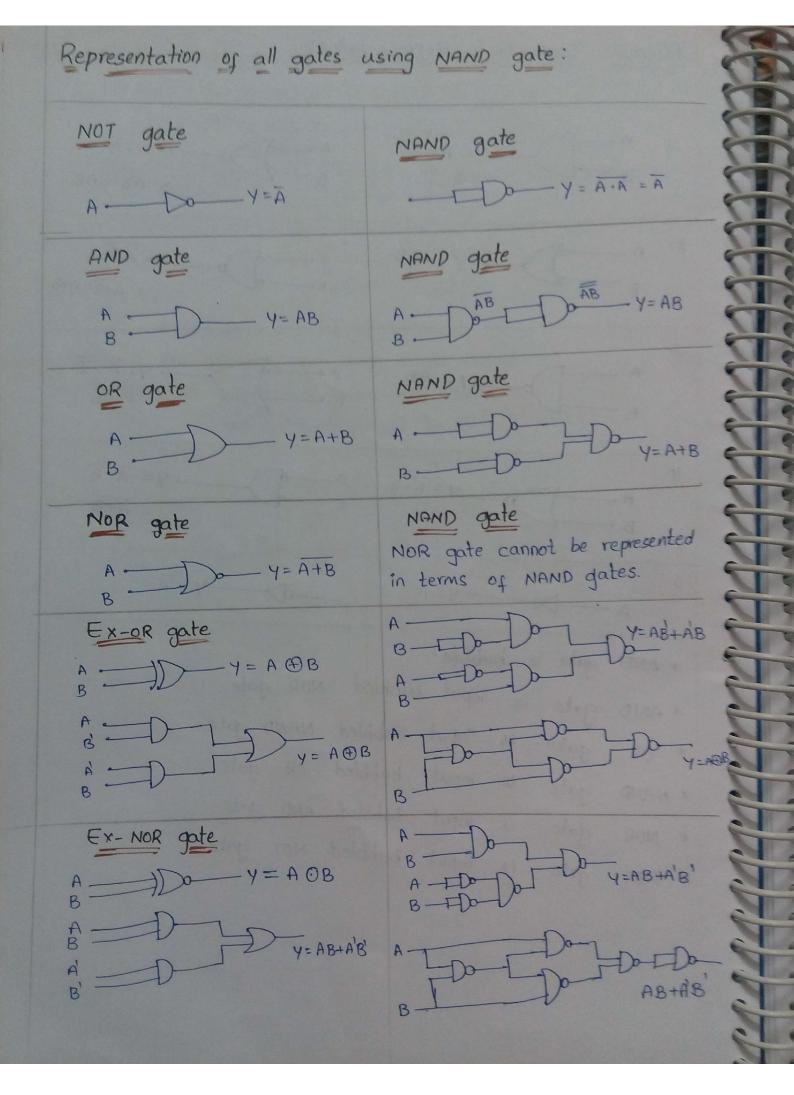

- AND Gate 1) Basic Gates ( OR Gate NOT Gate.

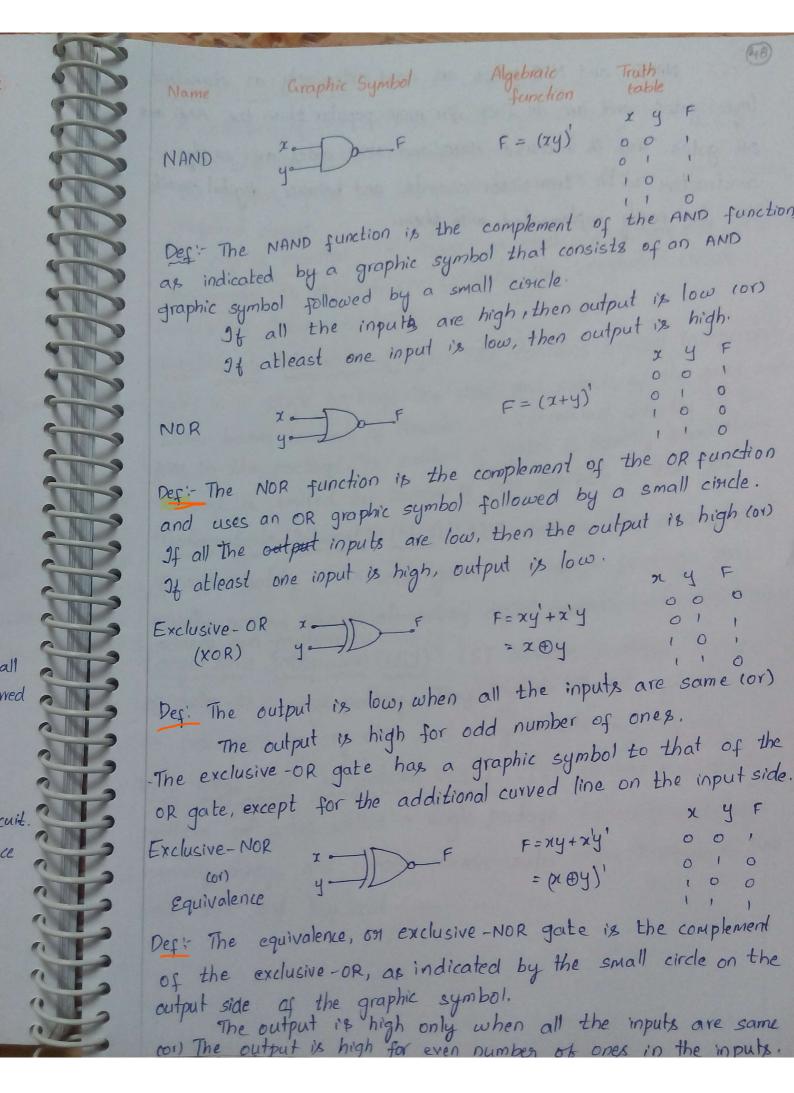

- -NAND Gate 2) Universal Gates - NOR Gate

- EX-OR Gate 3) Special Gates - EX-NOR Gate.

Scanned by CamScanner

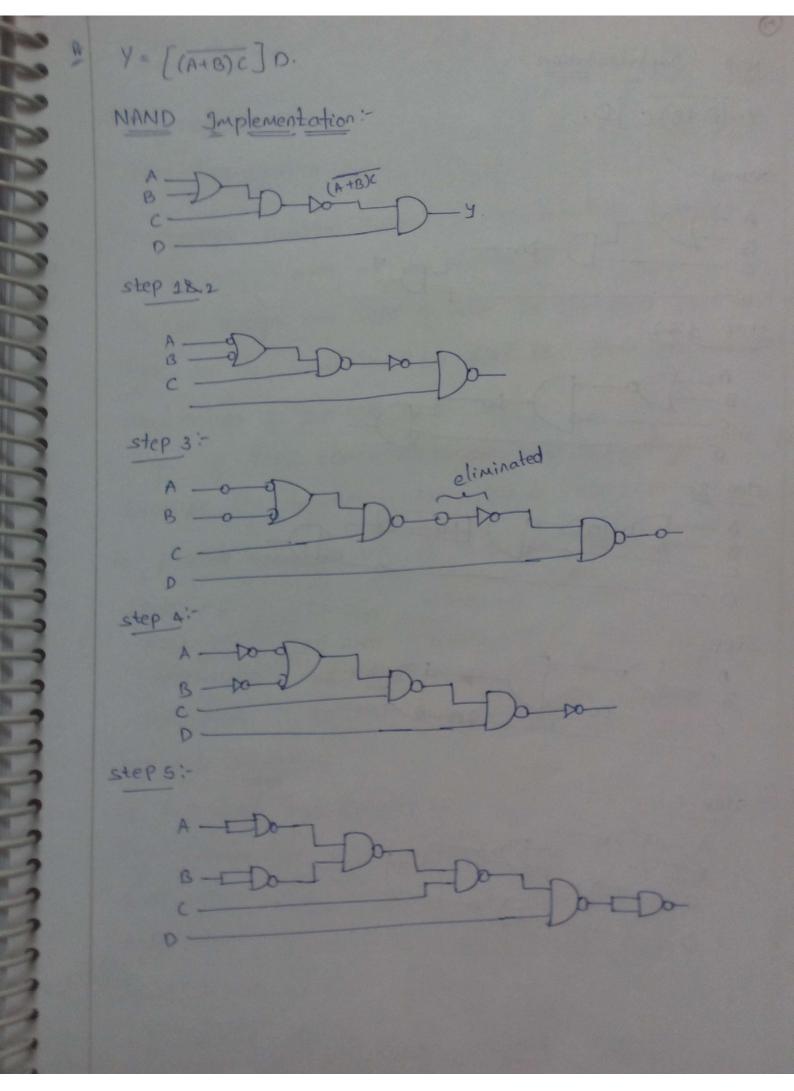

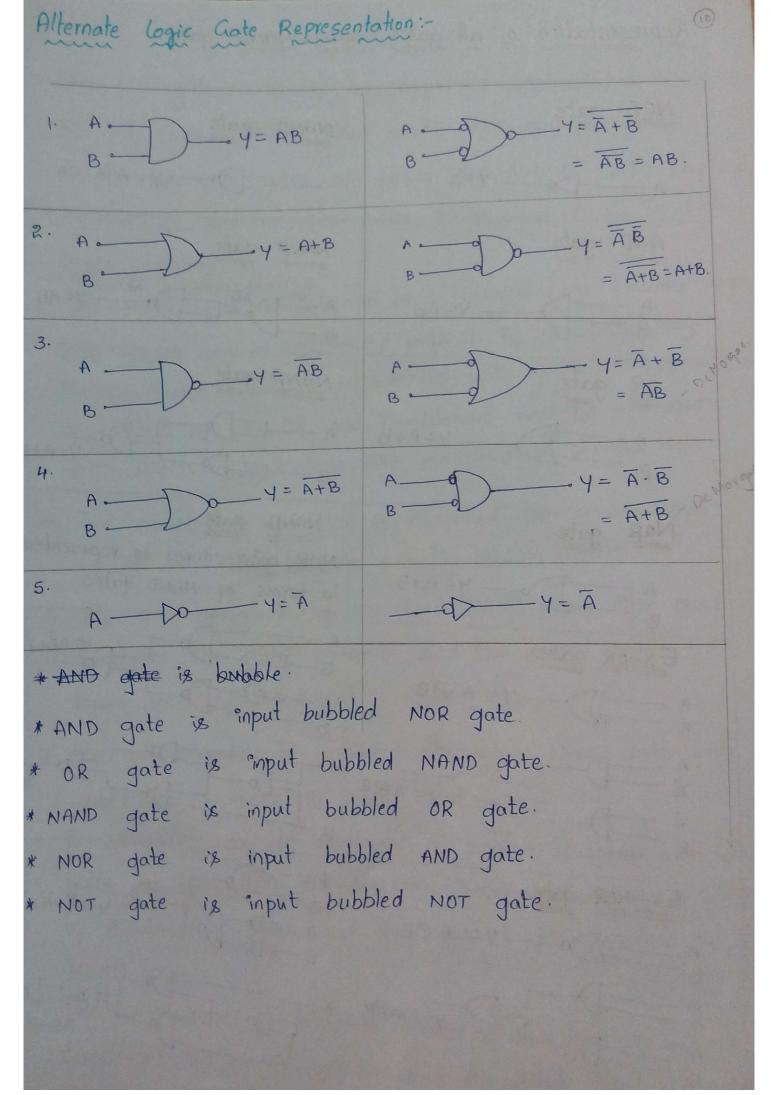

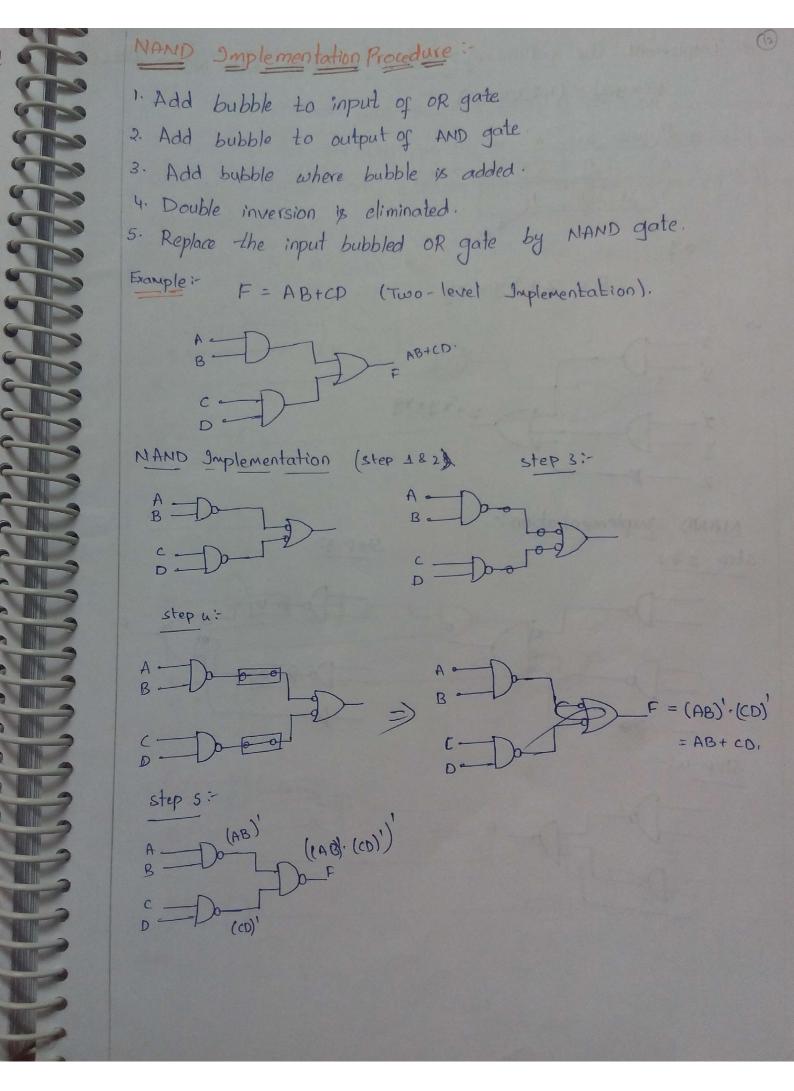

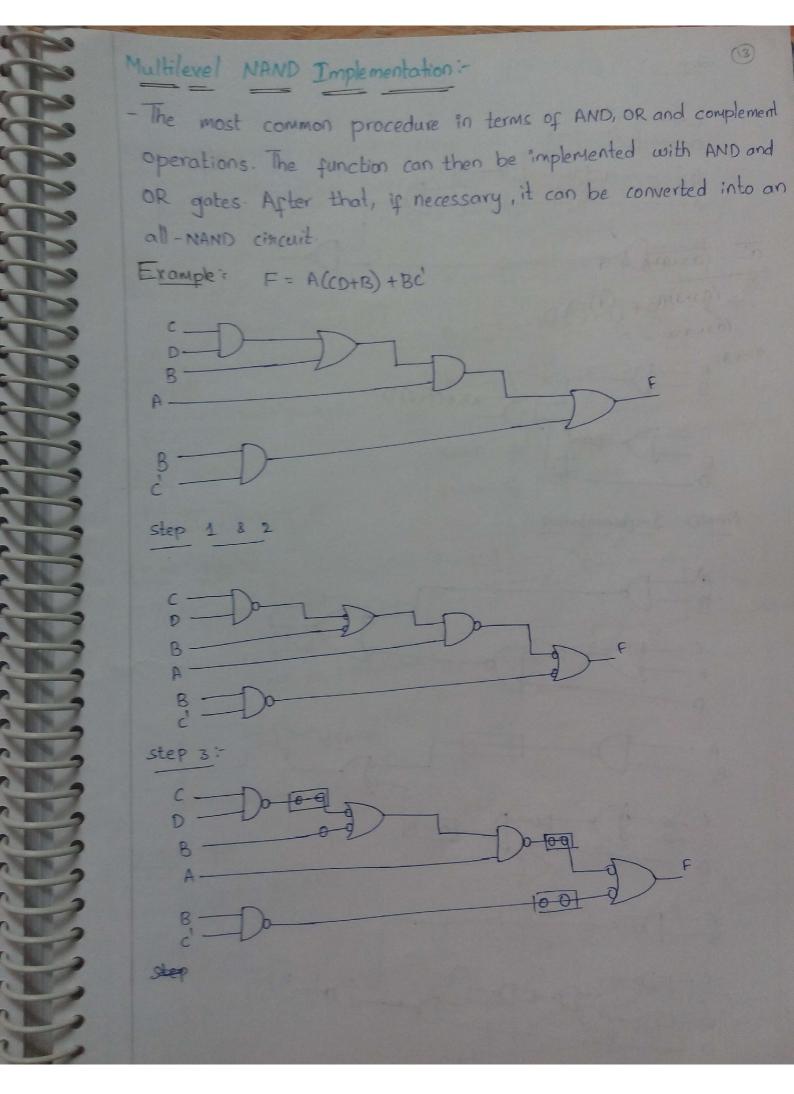

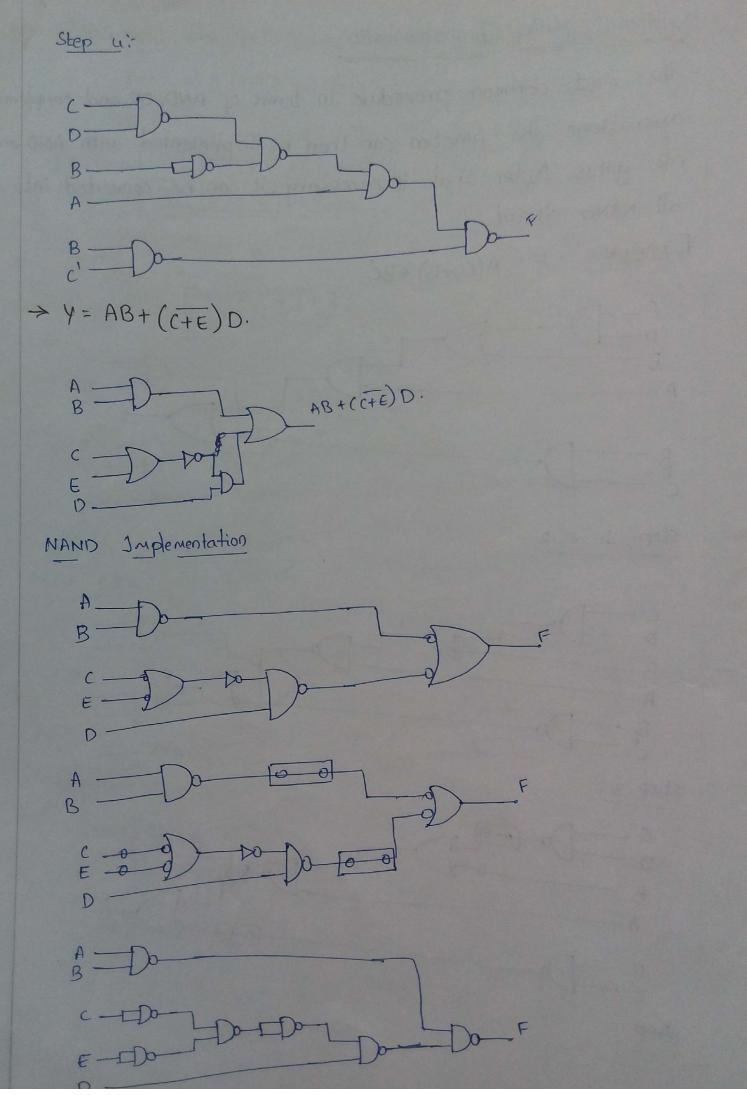

- lo facilitate the conversion to NAND logic, it is convenient to define an alternative graphic symbol for the gate. - Two equivalent graphic symbols for the NAND gate one shown in below 1 = 1 = (xyz) 42 ) (242) 18) Jovert-OR (a) AND - invert tig. Two graphic symbols for a three-input - The AND-invert symbol consists of an AND graphic Symbol followed by a small circle negation indicator referred to as a bubble. \*- Alternatively, it is possible to represent a NAND gate by an OR graphic symbol that is preceded by a bubble in - The invert-or symbol of the NAND gate follows DeMorganis each input. theorem and the convention that the negation indicator (bubble) denotes complementation. - The two graphic symbolis representations are useful in the analysis and design of NAND circuits - When both symbols are mixed in the same diagram, the circuit is said to be in mixed notation. -> Two-level implementation:

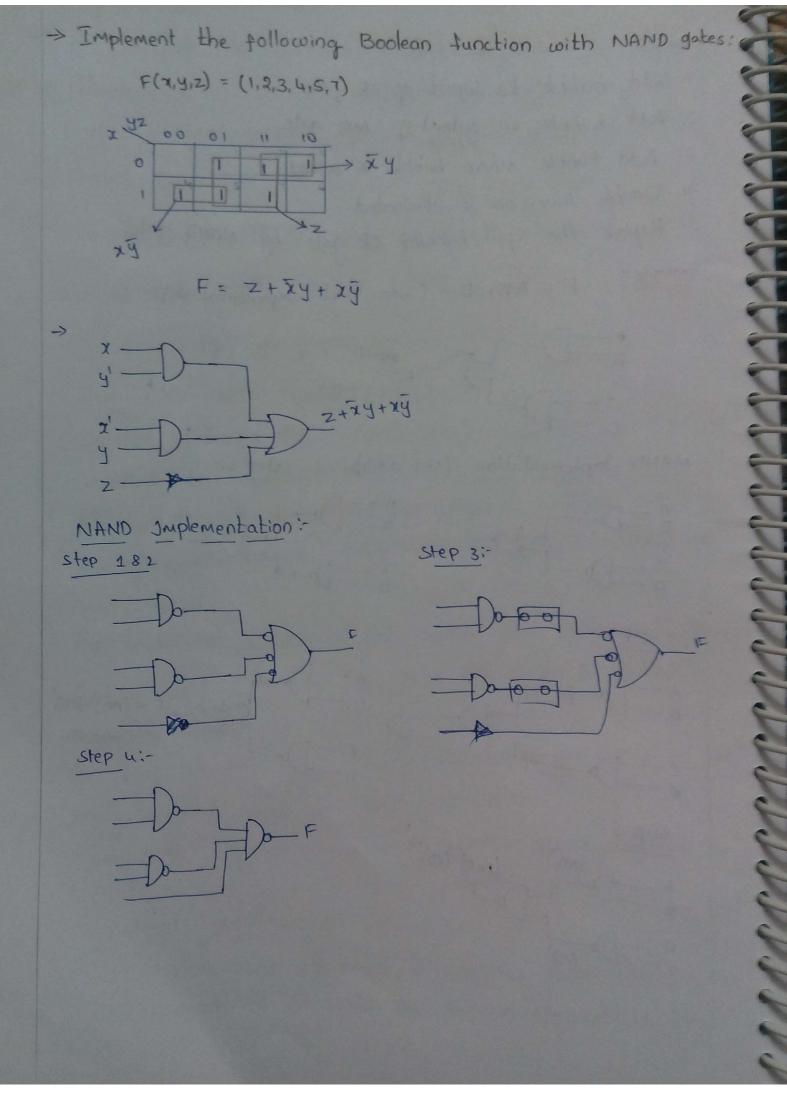

\* The implementation of Boolean functions with NAND gates

nequines that the functions be in sum-of-products form.

Scanned by CamScanner

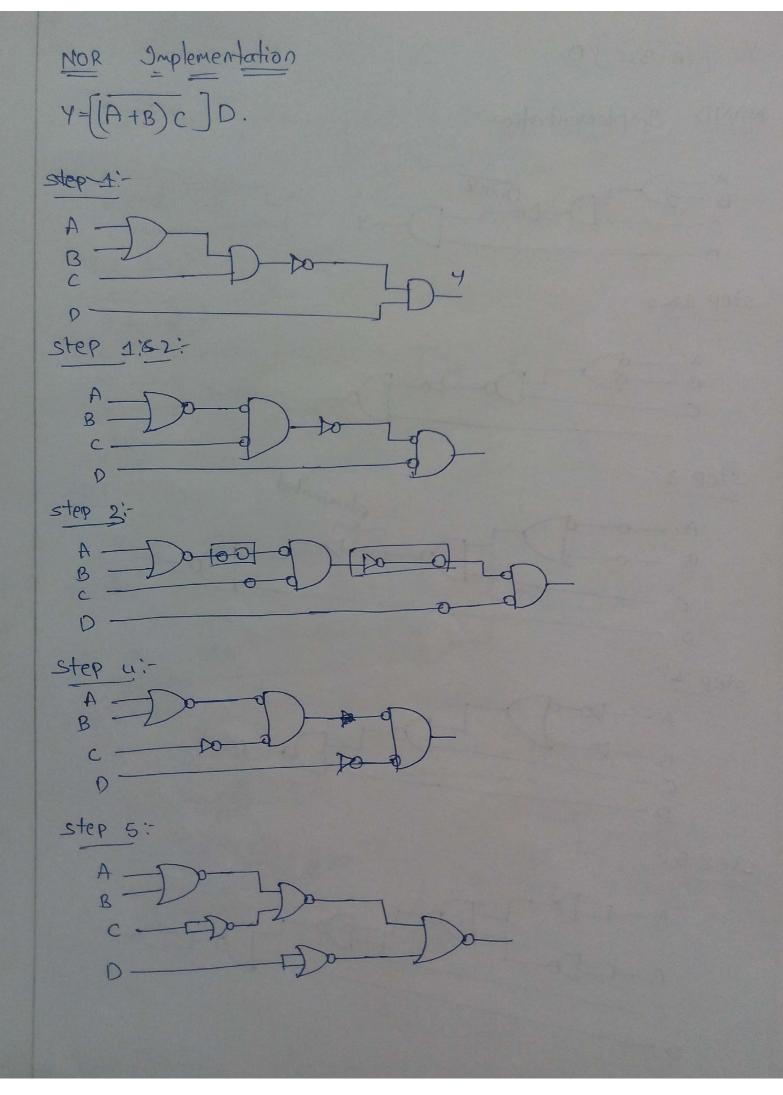

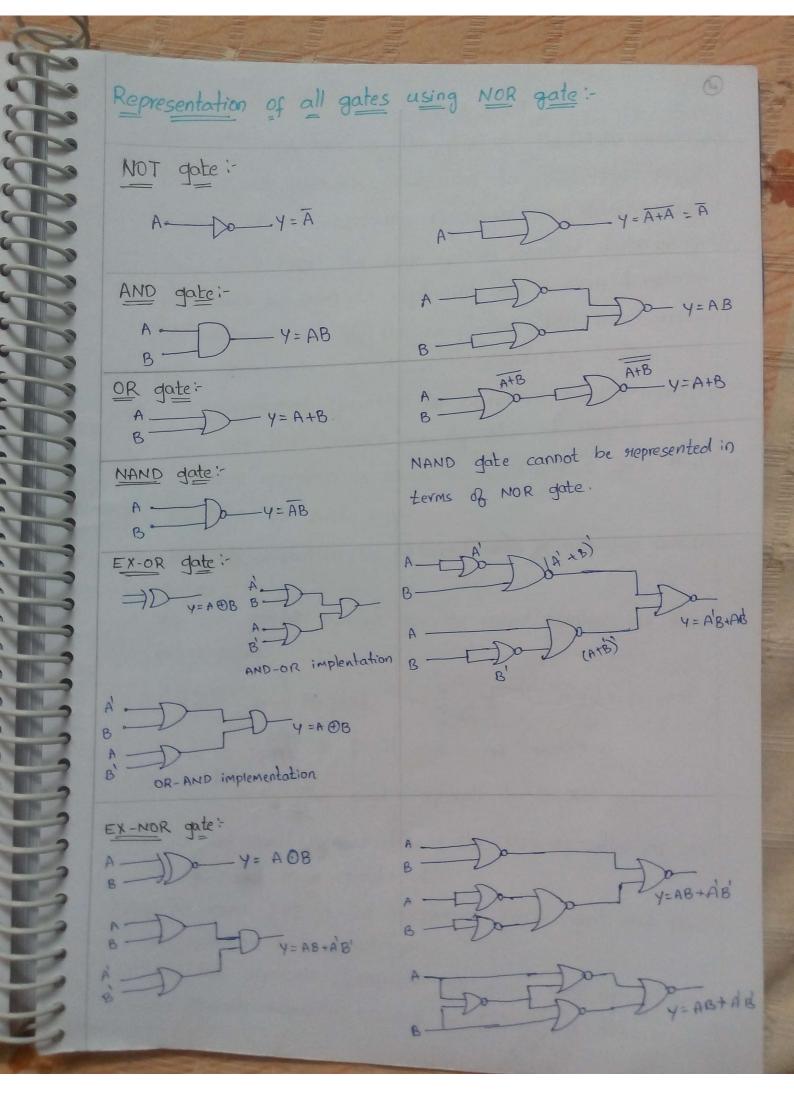

## NOR Implementation:

- The NOR operation is the dual of the NAND operation.

Therefore, all procedures and rules for NOR logic are the duals of the corresponding procedures and rules developed for NAND logic. The NOR gate is another unitersal gate that can be used to implement any Boolean function.

- The implementation of the complement, AND, OR operations with NOR gates is shown in above tig.

1. The complement operation is obtained from a one-input.

NOR gate that behaves exactly like an inverter.

2. The AND operation is obtained with a NoR gate that has inverters in each input:

3. The or operation is obtained with a nequines two NOR gates.

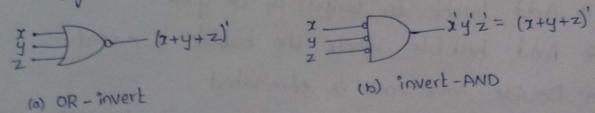

\* The two graphic symbols for the mixed notation are shown in below figure.

tig: Two graphic symbols for the NOR gate.

- (a) The oR-invert symbol defines the NOR operation as an OR followed by a complement.

- (b) The invert-AND symbol complements each input and then performs an AND operation.

- The two symbols designate the same NOR operation and are logically identical because of DeMorganis theorem.

## > Two-level implementation

- A two-level implementation with NOR gates requires that function be simplified into product-of-sums form.

- Product- of-Sums expression is obtained from the map by combining the o's and complementing.

- A product-of-sums expression is implemented with a first level of or gates that produce the sum terms followed by a second-level AND gate to produce the product.

- The transformation from the OR-AND diagram to a NOR diagram is acheived by changing the OR gates to NOR gates with OR-invert graphic symbol and the AND gate to a NOR gate with an invert-AND graphic symbol. A single literal term going into the second-level gate must be complemented.

## → NOR Implementation Procedure:

- 1. Add bubble to input of AND gate.

- 2. Add bubble to output of or gate

- 3. Add bubble where the bubble is added.

- 4. Double inversion is eliminated

- 5. Replace the input bubbled AND gate by NOR gate.

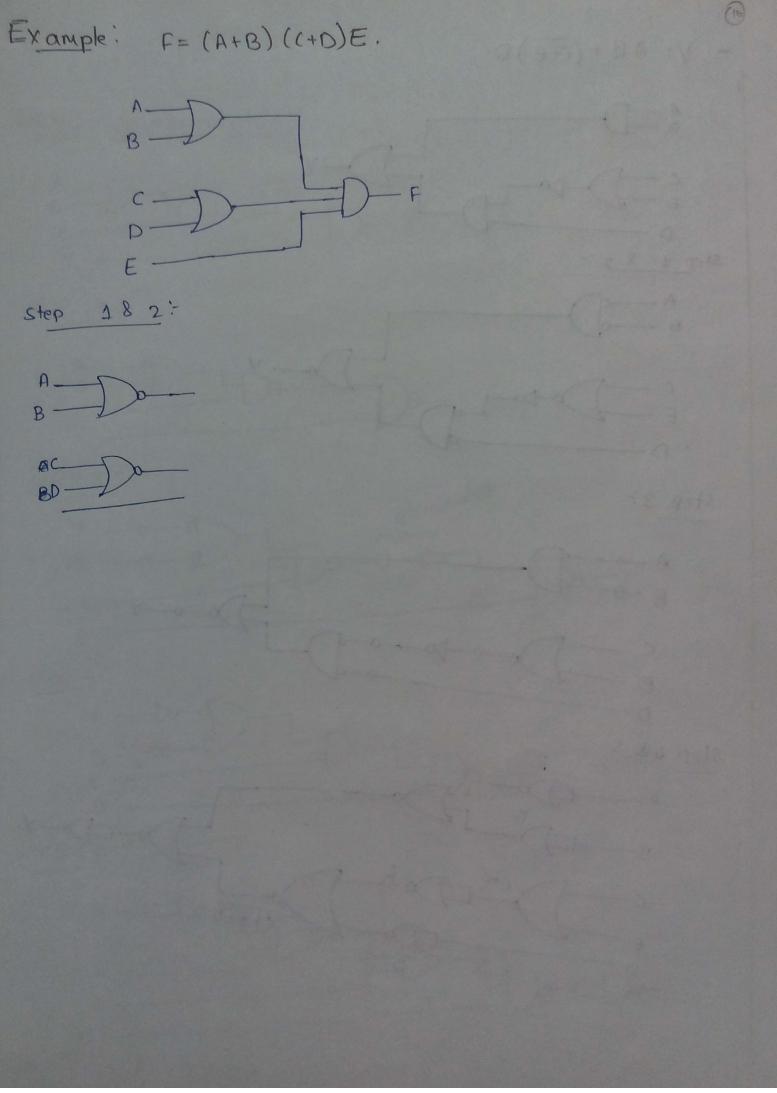

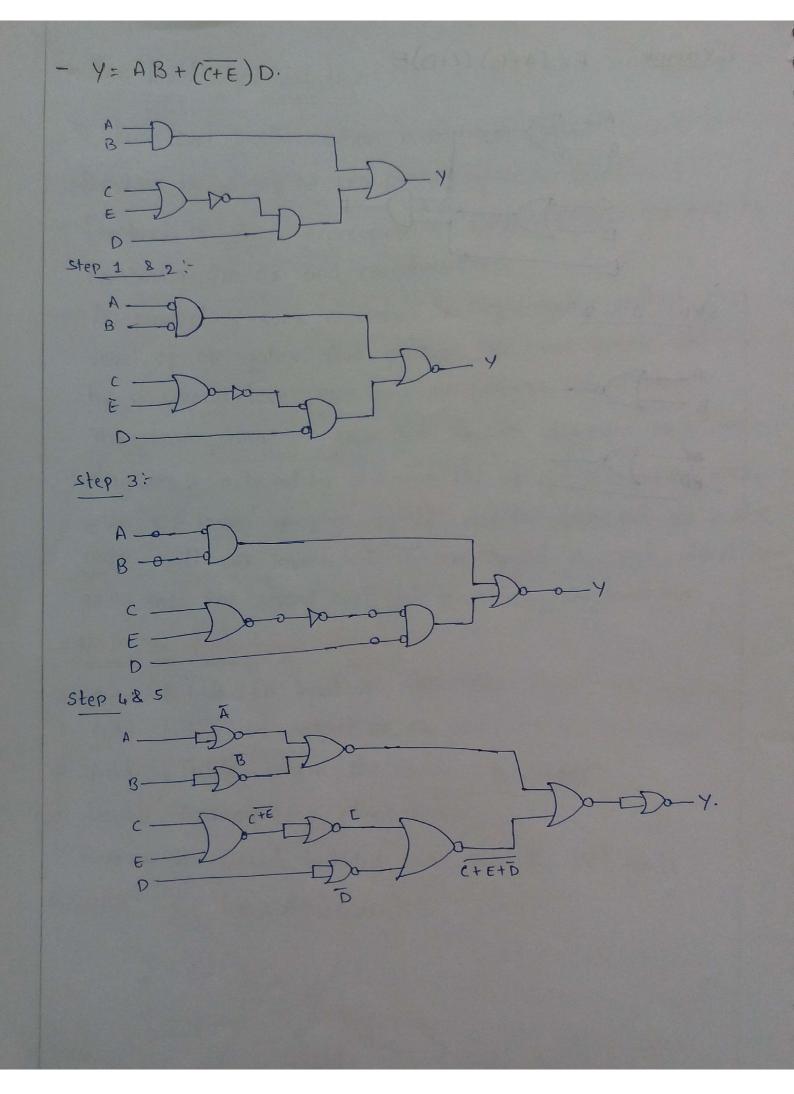

Example: F= (AB+AB) (C+D).

A'

B

C