Digital Logic Design And Computer Organization

### UNIT-I

# **Computer Types**

#### Computer:-

- Computer is a fast electronic calculating machine that accepts digitized input information ,processes it according to a list of internally stored instruction ,and produces the result out put information.

- Here list of instructions called a computer program and the internal storage is called computer memory.

#### Computer Organization

• Computer organization is defined as the way the hardware components operate and the way they are connected together to form the computer system.

# **Computer Types**

- There are many types of computers that differ many factors like size, cost , performance and use of computer.

- 1)personal computer:

-having processing and storage units ,display ,audio and keyboard.

-used in homes ,schools and business offices.

2)Notebook computers:

-compact version of personal computer .

-all components are packed into a single unit with the size of briefcase.

#### 3)Work sattions :

- -same as desktop but its having high resolution graphics I/O capability.

- -More computational power than personal computers.

- -Used in Engineering applications and Interactive applications.

# **Computer Types**

#### 4)Enterprise Systems or Main Frames :

- Used for business data processing in medium to large corporations that require much more computing power and storage capacity than workstations.

# 5)Servers:

-it contains sizable data units.

-servers capable of handling large volumes of requests to access the data.

- used in education ,business and user personal communities.

# 6)Super Computers:

-used for large scale numerical calculations.

-Examples weather forecasting ,and aircraft design and simulation.

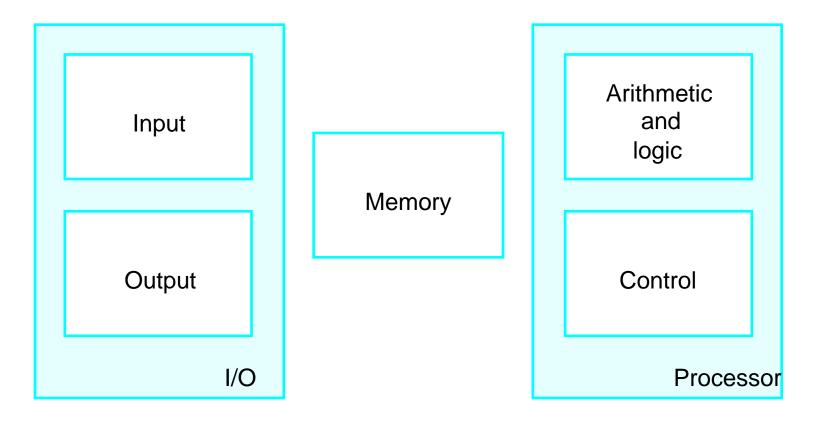

- Computer Consists of Five functionally independent parts:

- 1) Input 2) Memory 3) ALU 4) Output 5)Control Unit

- -input unit accepts coded information from human operators from electromechanical devices such as keyboard or from other computers over communication lines.

- -The received information is either stored in memory or used by ALU to perform the desired operation.

- -The processing steps are determined by a program stored in the memory.

- -Finally results are sent back to the outside world through the output unit. -All the above operations are coordinated by the control unit.

Figure 1.1. Basic functional units of a computer.

• Instructions or Machine instructions are explicit commands responsible for

The transfer of information with in a computer as well as between the computer and its I/O devices.

It specify the ALU operations to be performed.

- A list of instructions that perform a task is called a program.

- High level program called source program.

- Machine level program called object program.

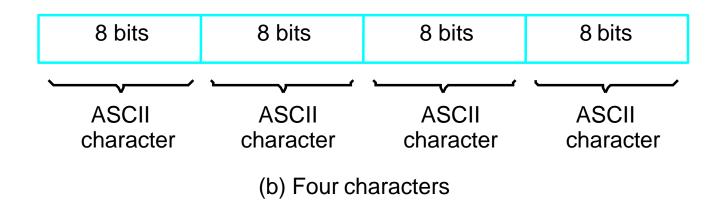

- Information is encoded in the form of 0's and 1's.

# • Input Unit:

-accepts coded information through input unit.

-when ever a key is pressed the corresponding letter or digit is automatically translated into its corresponding binary code and transmitted to memory or processor.

-other input devices like joysticks ,mouse , microphone ,trackball etc.

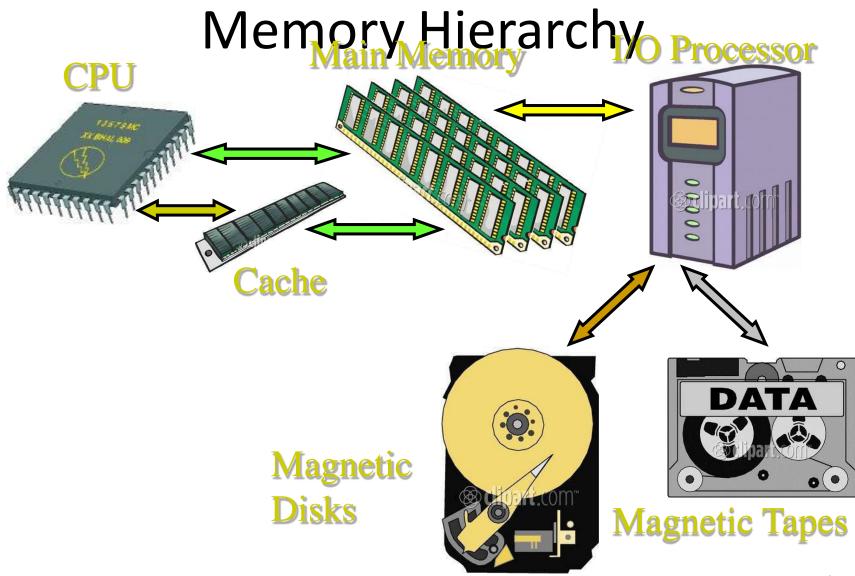

# • Memory Unit:

-Function of memory is to store programs and data.

- -there are two types of memory

- 1.Primary memory

- 2.Secoundary memory

- **Primary Memory**

-primary memory is fast memory operates at electronic speeds.

- -memory is collection of semiconductor cells.

- -Each cell is capable of storing one bit information.

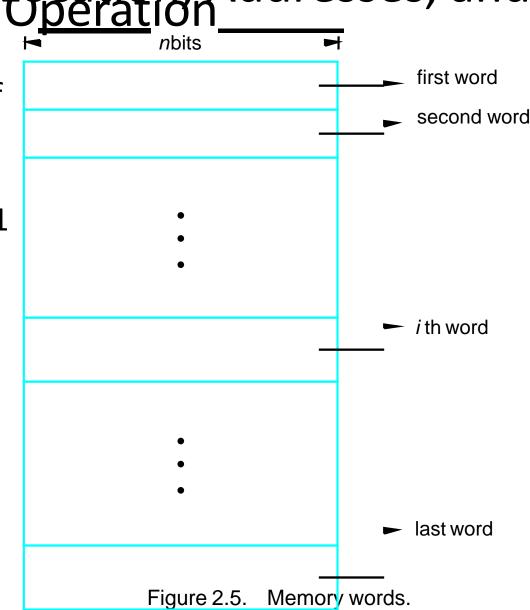

- -groups of fixed size cells called words.

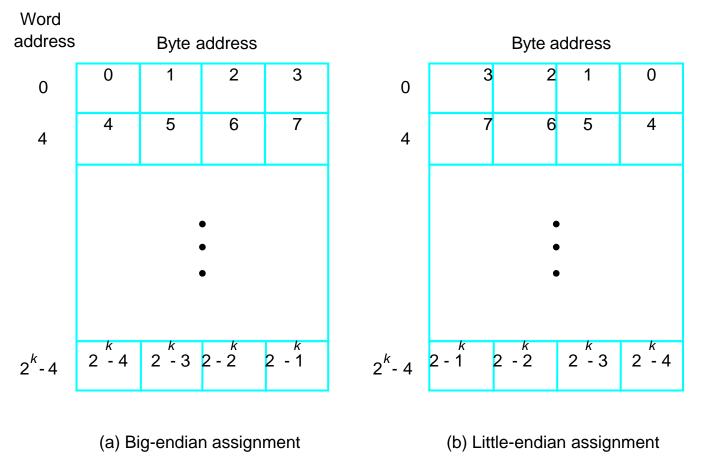

- -Each and every word is assigned with distinct addresses.

- -the number of bits in each word is often referred as the word length of the computer.

- -The memory in which any location can be reached in short and fixed amount of time after specifying its address is called random-accessmemory .

- -The time required to access one word is called memory access time.

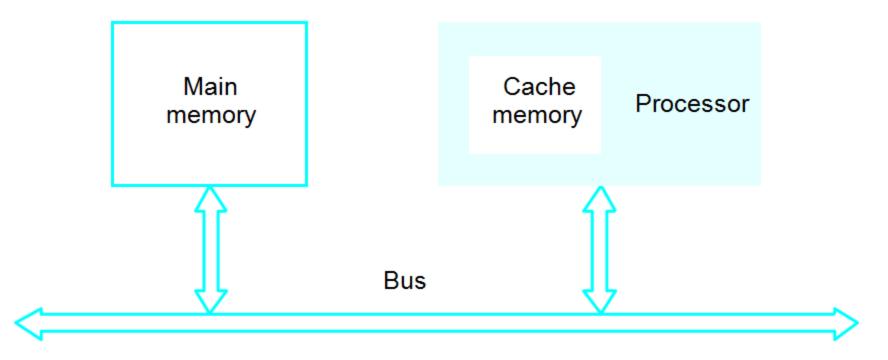

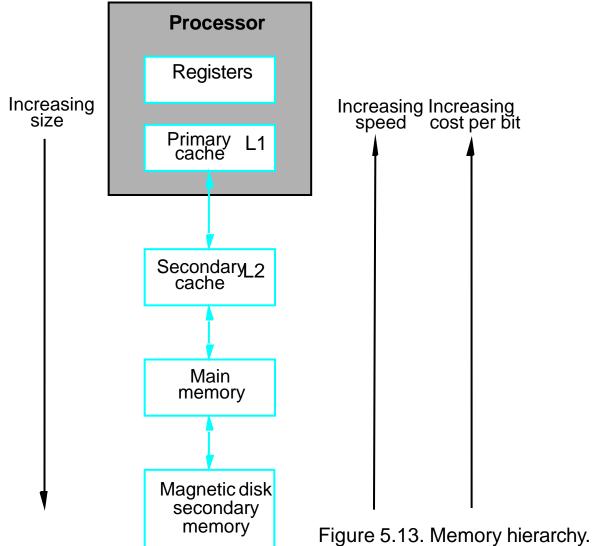

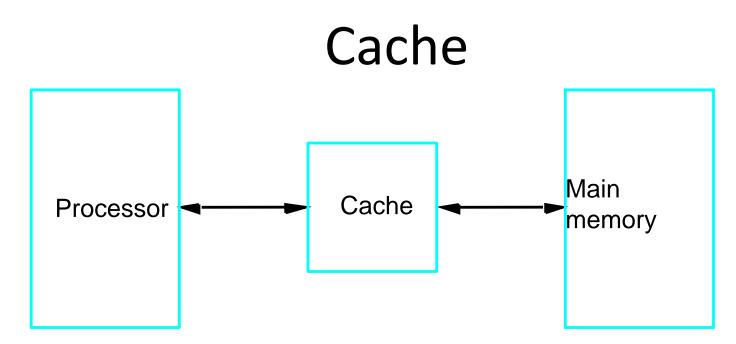

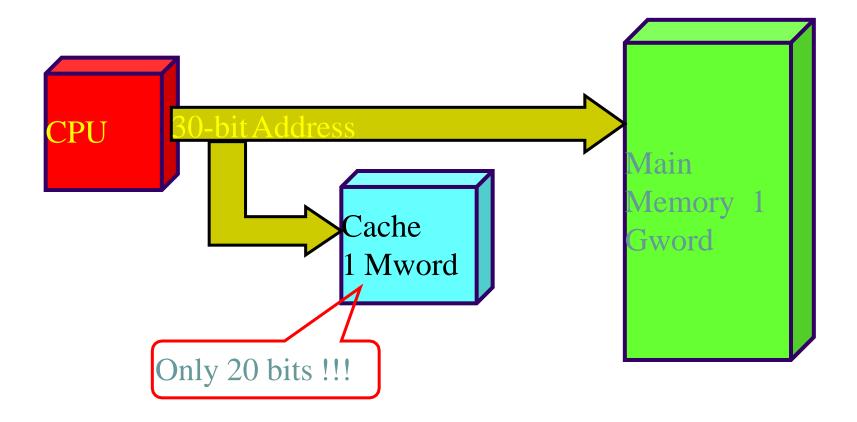

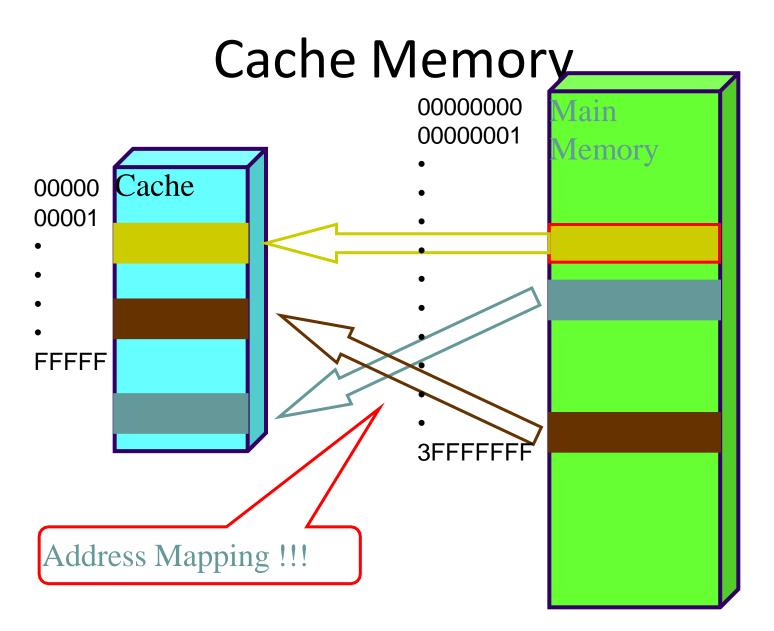

- -cache are small and fast accessing RAM units .these are tightly coupled with the processor to achieve high performance.

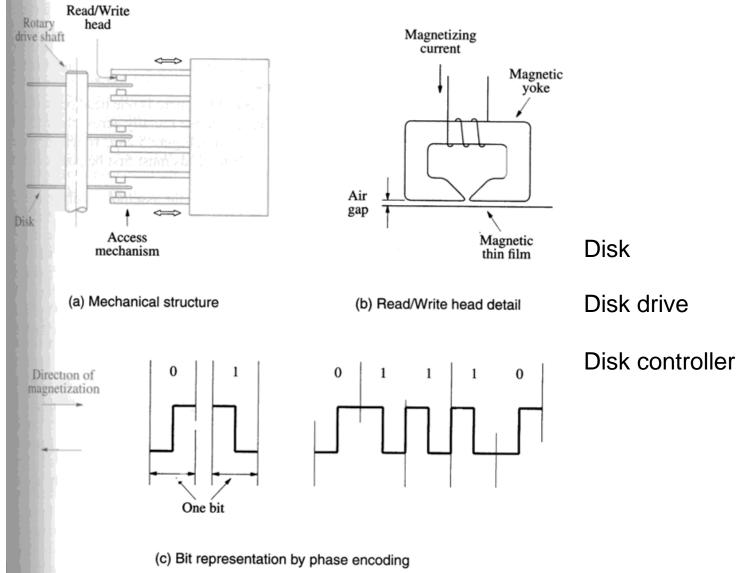

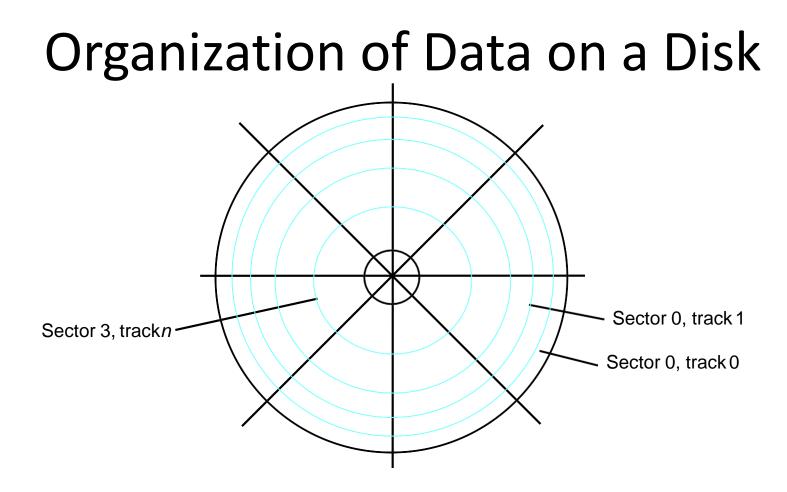

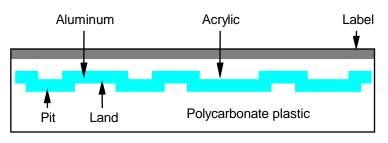

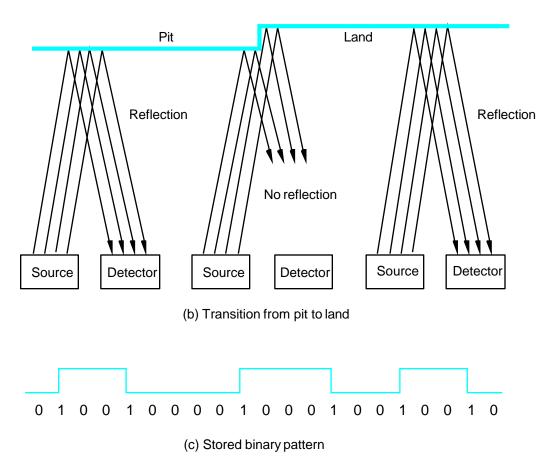

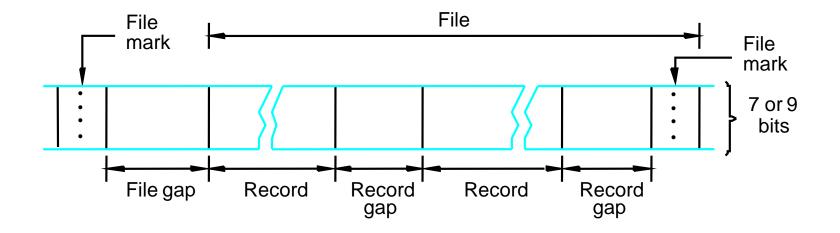

#### Secondary Storage:

-used to store large amount of data. Ex: tapes ,disk , optical disks.

# ALU:

- -Most of the computer operations are executed in the ALU of the processor.

- Ex: add,sub,mul,div

- -access time to registers are fast when compared to cache in memory hierarchy.

- -The CU and ALU are many times faster than other devices that connect to a computer system . So that a single processor to control many external devices.

# Output Unit:

- -The output unit is counterpart of input unit.

- -the main function is to send processed results to the outside world. Ex: printers, monitors.

## Control Unit:

- -The control unit is effectively the nerve center that sends control signals to the other units.

- -the memory ,ALU ,an I/O units store and process information and perform input and output operations. All these operations are carried out by CU.

# Operations of computer Summarized as:

- -the computer accepts information in the form of programs and data through an input unit and stores it in the memory.

- -information stored in the memory is fetched under program control into an ALU where it is processed.

- -processed information leaves the computer through an output unit.

- -All activities inside the machine are directed by the control unit.

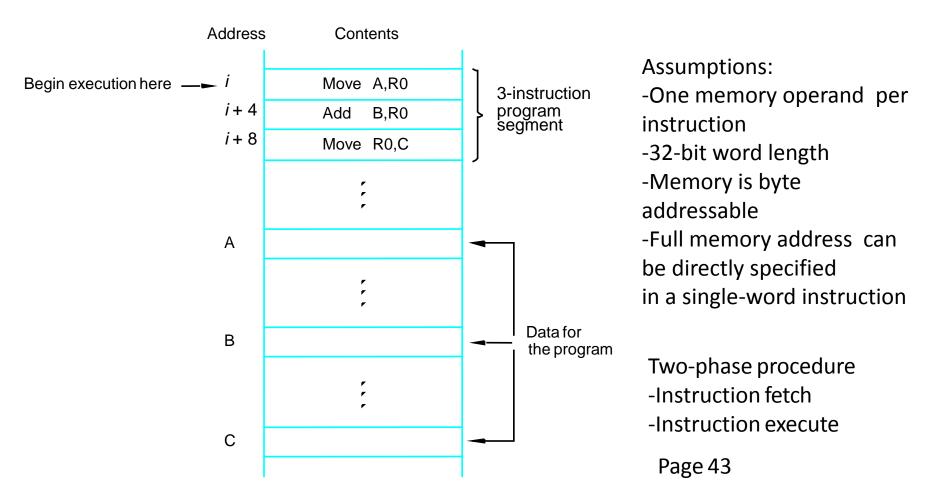

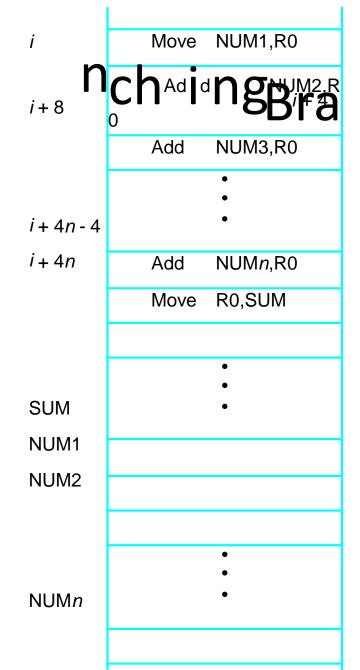

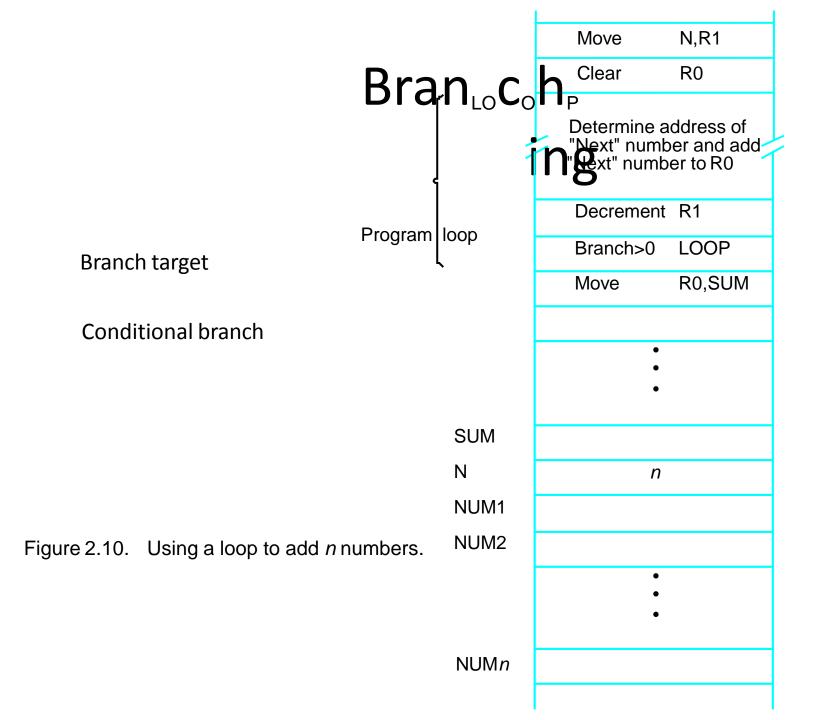

- Activity in a computer is governed by instructions.

- To perform a task, an appropriate program consisting of a list of instructions is stored in the memory.

- Individual instructions are brought from the memory into the processor, which executes the specified operations.

- Data to be used as operands are also stored in the memory.

- An Instruction : Add LOCA, R0

- Add the operand at memory location LOCA to the operand in a register R0 in the processor.

- Place the sum into register R0.

- The original contents of LOCA are preserved.

- The original contents of R0 is overwritten.

- Instruction is fetched from the memory into the processor the operand at LOCA is fetched and added to the contents of R0 the resulting sum is stored in register R0.

• Due to performance reasons the above instruction is implemented into two instructions:

Load LocA, R1 Add R1,R0

• Whose contents will be overwritten?

# Registers

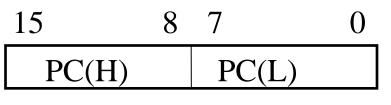

- 1) Instruction register (IR)

- 2) Program counter (PC)

- 3) General-purpose register  $(R_0 R_{n-1})$

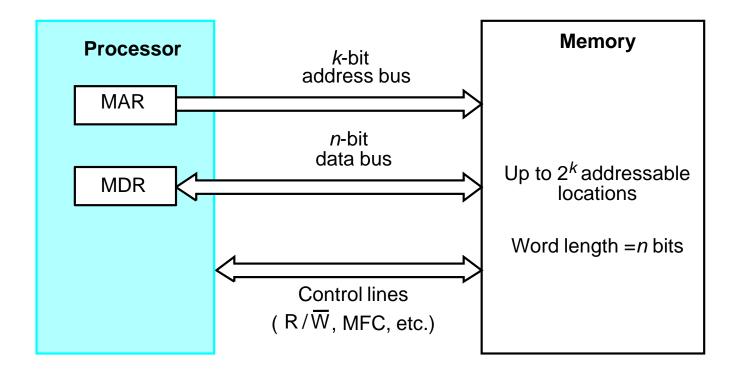

- 4) Memory address register (MAR)

- 5) Memory data register (MDR)

# **Operating Steps**

- Programs reside in the memory through input devices

- PC is set to point to the first instruction

- The contents of PC are transferred to MAR

- A Read signal is sent to the memory

- The first instruction is read out and loaded into MDR

- The contents of MDR are transferred to IR

- Decode and execute the instruction

- Operating Steps(Cont..)

- Get operands for ALU

- ➢ General-purpose register

- ≻ Memory (address to MAR Read MDR to ALU)

- Perform operation in ALU

- Store the result back

- To general-purpose register

- ≻ To memory (address to MAR, result to MDR Write)

- During the execution, PC is incremented to the next instruction

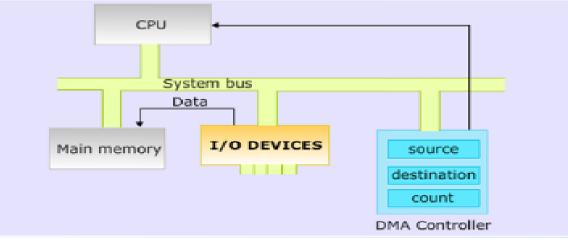

## Interrupt

- Normal execution of programs may be preempted if some device requires urgent servicing.

- The normal execution of the current program must be interrupted the device raises an *interrupt* signal.

- Interrupt-service routine

- Current system information backup and restore (PC, general-purpose registers, control information)

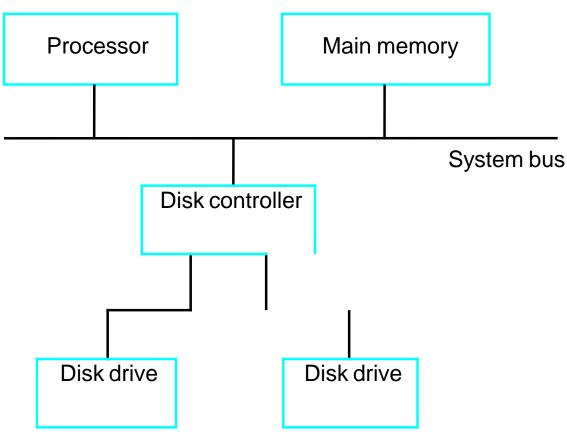

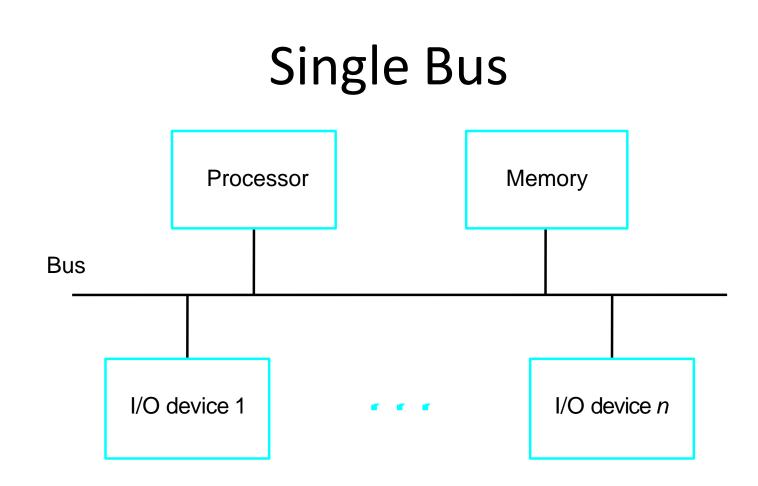

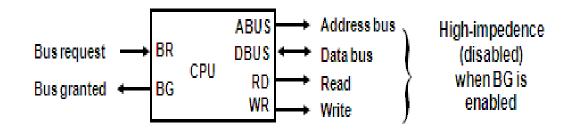

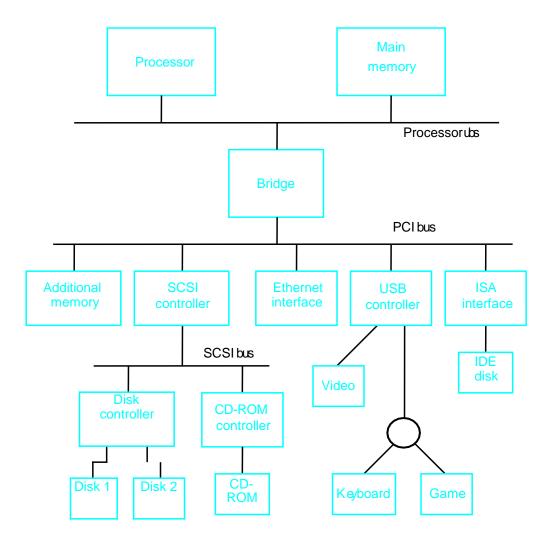

### **Bus Structures**

- To achieve good performance of a computer system all the computer units can transfer one word of data at a time.

- All the bits of a word transfer in parallel, that is the bits are transferred simultaneously over many lines one bit per line.

- There are many ways to connect different parts inside a computer together.

- A group of lines that serves as a connecting path for several devices is called a *bus*.

- A bus that connects major components is called system bus.

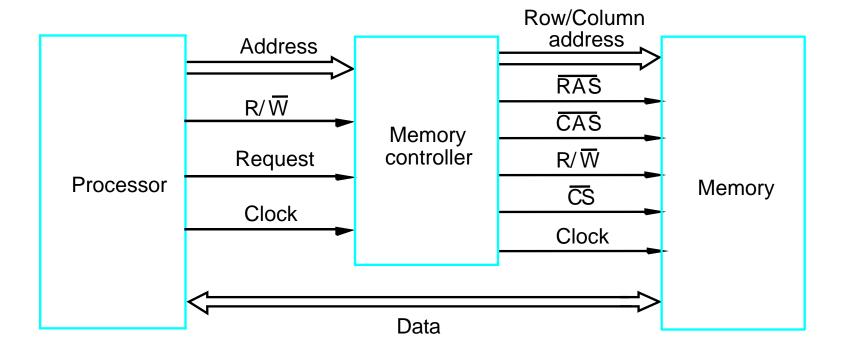

- System bus is divided into three functional groups : Address bus , data bus , control bus.

- Only two units can use bus structure at any point of time.

# Types of Buses

- There are different 9 type of buses

- 1) System bus

- 2) Single bus

- 3) Multiple Bus

- 4) Internal bus

- 5) External Bus

- 6) I/O Bus

- 7) Synchronous Bus

- 8) Asynchronous Bus

- 9) Back pane bus

# Types of Buses

#### 1)System Bus:

- System Bus Contains Data bus , Address Bus , Control Bus Data Bus:

- Data bus consists of 8,16,32 or more parallel signal lines.

- These lines are used to send the data to memory and output ports and to receive data from memory and input ports.

- It is a bi-directional bus.

- Address Bus:

- It is an Unidirectional bus.

- The address bus consists of 16, 20, 24 or more parallel signal lines.

- The cpu sends out the address of the memory location or I/O ports that is to be written to or read from.

- Control Bus:

- The Control lines regulate the activity on the bus.

- Ex: MEMW, MEMR, IOR, IOW, INTR etc....

#### 2) Single-bus

### Speed Issue

•Different devices have different transfer/operate speed.

- •If the speed of bus is bounded by the slowest device connected to it, the efficiency will be very low.

- •How to solve this?

- •A common approach use buffers. to smooth timing differences between devices. Ex: processor and printer data transfer.

#### Advantages:

•The main advantage of single bus structure is its low cost and flexibility for attaching peripheral devices.

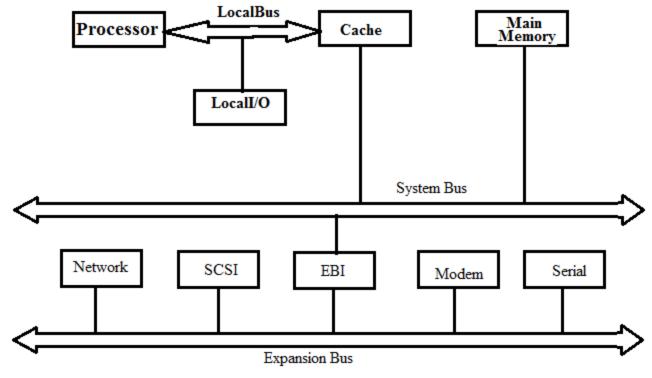

#### 3) Multiple Bus:

- Multiple bus Connection uses more number of different bus to connect the components.

- Generally it uses local bus, system bus, expanded bus, high speed bus.

- Multiple buses are used to transfer video and graphics type of data.

Fig: Multiple Bus Structure

#### Internal Bus:

- An internal bus connects all the internal components of a computer to the motherboard it is also called localbus.

- The internal bus of CPU connects the internal circuitry of the CPU. External Bus:

- An External bus connects external peripherals to the mother boaed.

- Ex: USB.

#### I/O Bus:

- I/O bus is used to link between the processor and several peripherals . Synchronous Bus:

- All devices derive timing information from a common clock signal then synchronous bus is used.

#### Asynchronous Bus:

• All devices derive timing information from a independent clock signal then Asynchronous bus is used.

#### Backplane Bus:

- A backplane or backplane system is a circuit board that connects several connectors in parallel to each other.

- It s used as a back bone to connect several system modules to make up a complete computer system.

### Software

- To execute user application programs a computer contains a software called system software.

- System software is a collection of programs that are executed to perform functions like :

- 1) Receiving and interpreting user commands.

- 2) Entering and editing application programs and storing them as files in secondary storage device.

- 3) Managing the storage and retrieval of files in secondary storage devices.

- 4) Running Standard Application Programs such as Word processor, Spread Sheets or games with data supplied by the user.

- 5) Controlling I/O Units to receive input information and produce output results.

- 6) translating programs from source form prepared by the user into object form consisting of machine instructions.

# Software

- 7) Linking and running user-written application programs with existing standard library routines such as numerical computation programs.

- Text editor ,Compiler , operating system are examples of System software.

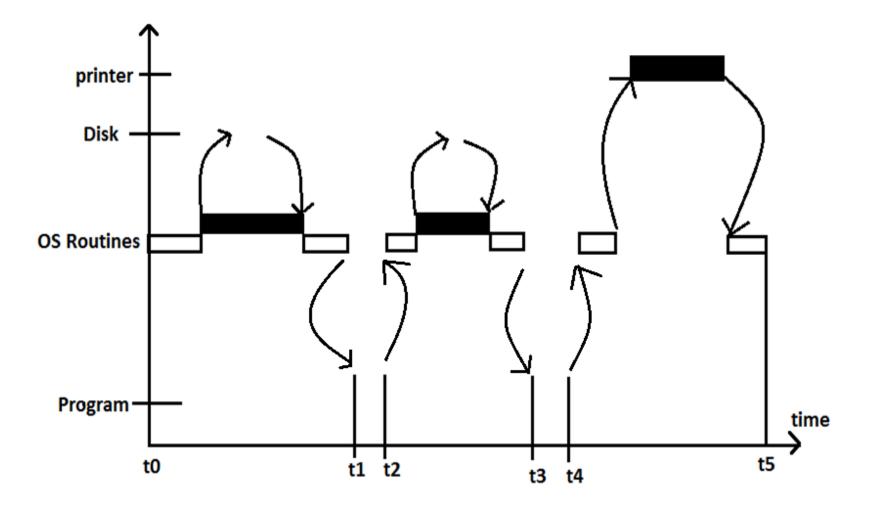

- The operating system is used to manage the execution of more than one application program at a time.

- Ex:- How the operating system manages the execution of application programs.

- 1) Transfer the file into the memory.

- 2) After Completion of transfer execution is started.

- 3) When execution of program reaches the point where the data file is needed, the program requests the operating system to transfer the data file from the disk to memory and passes control back to application program. Then proceed to perform the required computation.

- 4) when the computation is completed the application program sends a request to os .then os sends result to printer to print.

#### Software

Fig: User program and OS routine Sharing of the processor

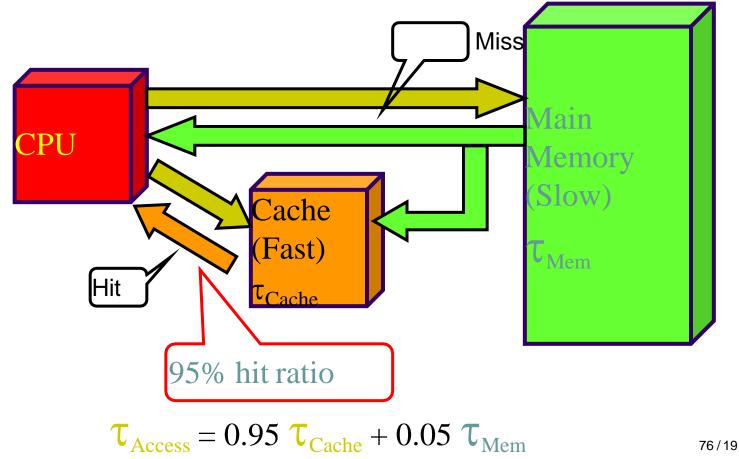

- The most important measure of a computer is how quickly it can execute programs.

- Three factors affect performance:

- Hardware design

- Instruction set

- Compiler

- The time required to compute a total process is call elapsed time.

- The time that the processor execute the program is called processor time.

- Elapsed time for the execution of a program depends on all units in a computer system.

•The processor time depends on the hardware involved in the execution of individual machine instruction.

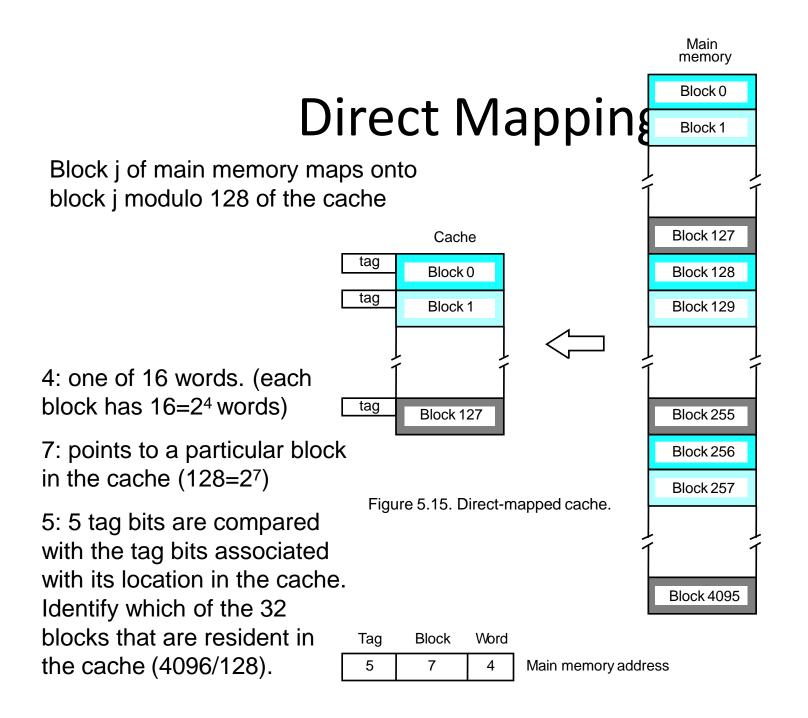

Figure 1.5. The processor cache.

### Processor Clock

- Processor circuits are controlled by a timing signal called a clock.

- The clock defines regular timing intervals, called clock cycles.

- To execute any machine instruction the processor divide the instruction into a sequence of basic steps ,such that each step can be completed in one clock cycle.

- Clock rate R=1/p here p is clock cycle length.

- Clock speed is measured in hertz(Hz)

#### **Basic Performance Equation:**

- T processor time required to execute a program that has been prepared in high-level language

- N number of actual machine language instructions needed to complete the execution (note: loop)

- S average number of basic steps needed to execute one machine instruction. Each step completes in one clock cycle

- R clock rate

- Note: these are not independent to each other

$$T = \frac{N \times S}{R}$$

#### How to improve T?

### Performance Measurement

- T is difficult to compute.

- Measure computer performance using benchmark programs. Ex: database ,compiler , game playing.

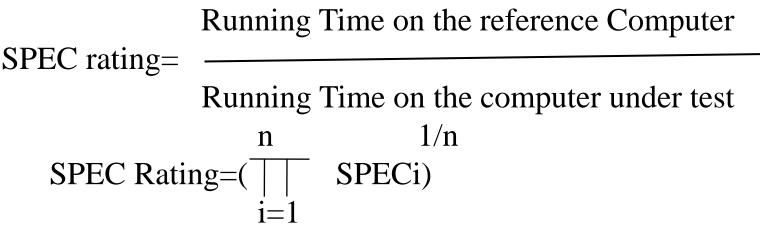

- System Performance Evaluation Corporation (SPEC) selects and publishes representative application programs for different application domains, together with test results for many commercially available computers.

- Reference computers like SPEC95, SUN SPARC, SPEC2000.

• n is the number of programs in the suite.

### Amdahl's Law

• Amdahl'a law is used to calculate the performance gain that can be obtained by improving some portion of a computer.

Speed up =  $\frac{\text{Performance for entire task using improved machine}}{\text{Performance for entire task using old machine}}$ Speed up =  $\frac{(\text{or})}{\text{Execution time for entire task using improved machine}}$ Execution time for entire task using original machine}

### Amdahl's Law

#### Fraction Enhanced(Fe):

- It is the fraction of the computation time in the original machine that can be converted to take advantage of the enhancement.

- Fe is always <=1.

#### Speedup Enhanced(Se):

- It tells how much faster the task would run if the enhancement mode was use for the entire program.

- Speed up enhancement is always >1.

|           | Execution Time old |   | Ето |

|-----------|--------------------|---|-----|

| Speedup = | <u> </u>           | = |     |

|           | Execution Time new |   | Etn |

#### Amdahl's Law

ETN = ETO X  $\left[ (1-Fe) + (Fe/Se) \right]$

Speed Up =  $\frac{E_{TO}}{E_{TO} \times [(1-F_e)+(F_e/S_e)]}$

# Multiprocessors and Multicomputers

#### Multiprocessor computer

- Execute a number of different application tasks in parallel

- Execute subtasks of a single large task in parallel

- All processors have access to all of the memory shared-memory multiprocessor

- Cost processors, memory units, complex interconnection networks

## Multicomputers

- Each computer only have access to its own memory

- Exchange message via a communication network messagepassing multicomputers

## DATA REPRESENTATION

- Information that a Computer is dealing with

- \* Data

- Numeric Data Numbers( Integer, real)

Non-numeric Data Letters, Symbols

- \* Relationship between data elements

- Data Structures

- Linear Lists, Trees, Rings, etc

- \* Program(Instruction)

#### •Number System

Nonpositional number system

- Roman number system

- Positional number system

- Each digit position has a value called a *weight* associated with it

- Decimal, Octal, Hexadecimal, Binary

- •Base (or radix) R number

- Uses R distinct symbols for each digit

- Example  $A_R = a_{n-1} a_{n-2} \dots a_1 a_0 \dots a_{-n}$

- V(A<sub>R</sub>) =

$$\sum_{i=-m}^{n-1} a_i R^i$$

Radix point(.) separates the integer portion and the fractional portion

- R = 10 Decimal number system, R = 2 Binary R = 8 Octal,

- R = 16 Hexadecimal

#### Decimal Number System

- The decimal number system in every day use employs the radix 10 system.

- The 10 symbols are 0,1,2,3,4,5,6,7,8 and 9.

- The string of digits 834.5 is interpreted as:  $8X10^2 + 3X10^1 + 4X10^0 + 5X10^{-1} = 834.5$

#### Binary Number System

- Binary number system uses the radix 2.

- The two digit symbols used are 0 and 1.

- The string of symbols 1001 is interpreted as:

$1 \ge 2^3 + 0 \ge 2^2 + 0 \ge 2^1 + 1 \ge 2^0 = 8 + 0 + 0 + 1 = 9$

- Octal Number System

- Octal Number System uses radix 8.

- The Symbols used to represent the octal number system is 0,1,2,3,4,5,6 and 7.

- The octal number is converted into decimal number system by forming the sum of the weighted digits.

Ex:

$$(736.4)_{8} = ?$$

= 7 x 8<sup>2</sup> + 3 x 8<sup>1</sup> + 6 x 8<sup>0</sup> + 4 x 8<sup>-1</sup>

= 7 x 64 + 3 x 8 + 6 x 1 + 4/8 = (478.5)\_{10}

#### Hexadecimal Number System

- The hexadecimal number system uses radix 16.

- The symbols used to represent the hexadecimal number system is 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E and F.

- The hexadecimal number is converted into decimal number system by forming the sum of the weighted digits.

Ex:

$$(F3)_{16} = ?$$

= F x 16<sup>1</sup> + 3 x16<sup>0</sup>

= 15 x 16 + 3=(243)\_{10}

Decimal to Other Number Systems

- Conversion from decimal to its equivalent representation in the radix r system is carried our by separating the number into its integer part and fraction part and converting each part separately.

- The conversion of a decimal integer into a base r representation is done by successive divisions by r and accumulation of the reminders.

- The conversion of a decimal fraction to radix r representation is accomplished by successive multiplication by r and accumulation of the integer digits obtained.

## Decimal to Binary Conversion:

#### **Ex:** (41.6875) $_{10} = (101001.1011)_2$

| Integer = $41$<br>41<br>20 1<br>10 0<br>5 0<br>2 1<br>1 0<br>0 1 | Fraction = $0.6875$<br>0.6875<br>x 2<br>1.3750<br>x 2<br>0.7500<br>x 2<br>1.5000<br>x 2<br>1.0000 |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| $(41)_{10} = (101001)_2$                                         | $(0.6875)_{10} = (0.1011)_2$                                                                      |

## Binary to Octal and Hexadecimal Conversion

- Each octal digit corresponds to three binary numbers i.e  $8=2^3$ .

- Each hexadecimal digit corresponds to four binary numbers i.e  $16=2^{4}$ .

#### Binary, octal, and hexadecimal conversion

| 1   | 2   | 7     | 5    | 4 3   | Binary |

|-----|-----|-------|------|-------|--------|

| 1 0 | 1 0 | 1 1 1 | 1011 | 00011 | Octal  |

| А   |     | F     | 6    | 3     | Hexa   |

BCD:

BCD is used to represent the decimal numbers system to binary number system

## COMPLEMENT OF NUMBERS

#### Two types of complements for base R number system:

- 1) (R-1)'s complement

- 2) R's complement

#### 1) The (R-1)'s Complement

- Number N in base r having n digits (r-1)'s complement is defined as  $(r^n 1) N$ .

- Subtract each digit of a number from (R-1)

Example

- 9's complement of  $835_{10}$  is  $164_{10}$

- 1's complement of  $1010_2$  is  $0101_2$ (bit by bit complement operation)

## COMPLEMENT OF NUMBERS

## 2) The R's Complement

- The r's complement of an n-digit number N in base r is defined as r<sup>n</sup>-N for N is not 0.

- Add 1 to the low-order digit of its (R-1)'s complement

Example

- 10's complement of  $835_{10}$  is  $164_{10} + 1 = 165_{10}$

- 2's complement of  $1010_2$  is  $0101_2 + 1 = 0110_2$

## Subtraction of unsigned numbers

- The subtraction of two n-digit unsigned numbers M-N (N is not zero)in base r can be done as follows:

- 1) Add the minuend M to the r's complement of the subtrahend N.this performs  $M+(r^n-N)=M-N+r^n$ .

- If M>=N, the sum will produce an end carry r<sup>n</sup> which is discarded, and what is left is the result of M-N.

- 3) If M<N, the sum does not produce an end carry and is equal to  $r^{n}$ -(N-M), which is the r's complement of (N-M). To obtain the answer in familiar form ,take the r's complement of the sum and place a negative sign in front.

# Subtraction of unsigned numbers

Example:

M=72532 N=13250

Here M>N

# 10's Complement of N \_\_\_\_\_86750

<sub>7</sub>159282

75532

End Carry Discard

#### Subtraction of unsigned numbers Example2: M<N M = 13250N = 7253213250 M =10's complement of N=27468 Sum = 40718

Answer is Negative 59282 =10's complement of 40718

## Subtraction of unsigned numbers

Example 3: X=1010100 Y=1000011 X= 1010100 2's Complement of Y= 0111101 Sum= 10010001 Answer of X-Y = 0010001

## Subtraction of unsigned numbers

Example 4: X = 1010100 Y=1000011 2's Complement of X = 0101100Sum = 1101111 There is no End Carry.

Answer is negative 0010001 = 2' Complement of 1101111

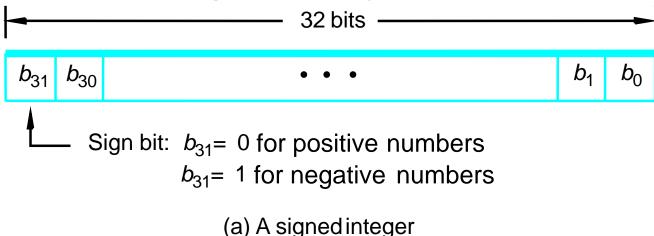

- Positive integers , including zero ,can be represented as unsigned numbers.

- The positive sign is represented as 0 and 1 for negative.

- The binary point is used to represent fractions ,integers , and mixed integer and fractions.

- There are two ways of specifying the position of the binary point in a register

- By giving it a fixed point representation

- By employing a floating point representation

- The fixed point method assumes that the binary point is always fixed in one position.

- The two positions most widely used are:

- 1) Binary point extreme left of the register

- 2) Binary point extreme right of the register

#### Integer Representation

- When a binary number is positive the sign is represented by 0 and the magnitude by a binary positive number.

- When the number is negative the sign is represented by 1 and the rest of the number may be represented in one of the three ways:

- 1) Signed magnitude representation

- 2) Signed 1's complement representation

- 3) Signed 2's complement representation

- **Example:** Represent +9 and -9 in 7 bit-binary number

Only one way to represent +9 = > 0.001001

Three different ways to represent -9:

In signed-magnitude:1 001001In signed-1's complement:1 110110In signed-2's complement:1 110111

- Complement

- Signed magnitude: Complement only the sign bit

- Signed 1's complement: Complement all the bits including sign bit

- Signed 2's complement: Take the 2's complement of the number, including its sign bit.

## Fixed Point Representation Arithmetic Addition in Signed Magnitude

#### Rules

- 1 . Compare their signs

- 2 . If two signs are the *same*,

ADD the two magnitudes - Look out for an overflow

- 3 . If *not the same*, compare the relative magnitudes of the numbers and then *SUBTRACT* the smaller from the larger .

- 4 . Determine the sign of the result

- Note: 1) The operation performed always addition including sign bit.

- 2) any carry out of sign bit is discarded.

- 3) Negative results are always in 2s complement form.

Example:

$\begin{array}{rrrr} + 6 & 00000110 \\ +13 & 00001101 \\ +19 & 00010011 \end{array}$

- +6 00000110

- -13 11110011

- -7 11111001

-6 11111010 +13 00001101 +7 00000111

- -6 11111010

- -13 11110011

- -19 11101101

## Fixed Point Representation Arithmetic Subtraction

## Rules:

- 1 ) To perform subtraction of two signed binary numbers take the 2's complement of the subtrahend (including sign bit) and add it to the minuend(including the sign bit) .

- 2) Discard the carry out of the sign bit position.

- The subtraction operation can be changed to addition if the sign of the subtrahend is changed.

$$(\pm A) - (-B) = (\pm A) + (+B)$$

$(\pm A) - (+B) = (\pm A) + (-B)$

# Fixed Point Representation Arithmetic Subtraction

- Example:

- (-6) (-13)=+7

take the 2'complement of -13 i.e +13=00001101 -6 11111010 +13 00001101 +7 100000111 Remove the End carry i.e 00000111=+7

## Overflow

- When two numbers of n digits each are added and then the sum occupies n+1 digits then we call overflow occurred.

- An overflow is a problem in digital computers because the width of a register is finite.

- Because of this reason many computes detect the occurrence of overflow problem and set a overflow flip flop.

- When two numbers are added the overflow is detected by using an end carry.

- An overflow can not occur after an addition if one number is positive and the other is negative .

- An overflow may occur if the two numbers added are both positive or both negative.

Example :

| carries : | 01        | carries: | 1 | 0         |

|-----------|-----------|----------|---|-----------|

| +70       | 0 1000110 | -70      |   | 1 0111010 |

| +80       | 0 1010000 | -80      |   | 1 0110000 |

| +150      | 1 0010110 | -150     |   | 0 1101010 |

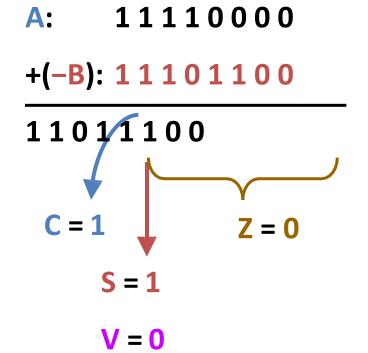

#### **Overflow Detection**

- An overflow is detected by observing the carry into the sign bit position and the carry out of the sign bit position.

- If these two carries are not equal an overflow is occurred.

- If the two carries are applied to an exclusive-OR gate, an overflow will be detected when the output of the gate is equal to 1.

## Floating-point Representation

- The floating-point representation of a number has two parts.

- The first part represents a signed , fixed-point number called mantissa .

- The second part designates the position of the decimal(or) binary point and is called the exponent.

#### m X r<sup>e</sup>

• The fixed point mantissa may be a fraction or an integer. Example:

+6132.789 is represented in floating point as : fraction=+0.613789 exponent=+04

## Floating-point Representation

- A floating point binary number +10011.11 is represented as: Fraction=01001111 Exponent=000101

Normalization:

- A floating point number is said to be normalized if the most significant digit of the mantissa is nonzero.

- The number can be normalized by shifting it three positions to the left and discarding the leading 0's.

Example:

- 00011010 is normalized as 11010000

- In the above example the three shifts multiply the number by  $2^3 = 8$  to keep the same number the exponent must be subtracted by 3.

## Floating-point Representation

- There are two standards to represent floating point numbers:1)ANSI

2)IEEE

- The ANSI 32 bit format is represented As: Byte Format:

Byte1Byte2Byte3Byte4SEEEE.IMMMMMMMMMMMMMMMMMMMMMImage: Second Se

S=Sign of Mantissa E=Exponent Bits in 2's complement M=Mantissa Ex: 13=1101=0.1101X2<sup>4</sup>

=00000100 11010000 0000000 00000000

$-17 = -10001 = -0.10001 X2^5 = 10000101 10001000 0000000 00000000$

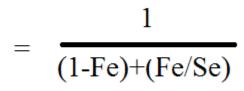

## **Error Detection Codes**

Parity System

- Simplest method for error detection

- One *parity* bit attached to the information

- Even Parity and Odd Parity

- Even Parity

- One bit is attached to the information so that the total number of 1 bits is an even number 1011001 0 1010010 1

- Odd Parity

- One bit is attached to the information so that the total number of 1 bits is an odd number

1011001 1 1010010 0

## **Error Detection Codes**

Fig: Error Detection With Odd Parity Bit

## UNIT-II

# Fundamentals of Boolean Algebra

- **Basic Postulates** ٠

- **Postulate 1 (Definition)**: A Boolean algebra is a closed algebraic system containing a set K of two or more elements and the two operators  $\bullet$  and +.

- Postulate 2 (Existence of 1 and 0 element): (a) a + 0 = a (identity for +), (b)  $a \bullet 1 = a$  (identity for  $\bullet$ )

- Postulate 3 (Commutativity): (a) a + b = b + a,

(b)

$$a \bullet b = b \bullet a$$

• Postulate 4 (Associativity): (a) a + (b + c) = (a + b) + c (b)  $a \bullet (b \bullet c) = (a \bullet b) \bullet c$

- *Postulate 5 (Distributivity)*: (a)  $a + (b \bullet c) = (a + b) \bullet (a + c)$  (b)  $a \bullet (b + c) = a \bullet b + a \bullet c$

- **Postulate 6 (Existence of complement):** •

(a)

$$a + \overline{a} = 1$$

(b)

Normally • is omitted.  $a • \overline{a} = 0$

## **Fundamentals of Boolean Algebra**

- Fundamental Theorems of Boolean Algebra

- Theorem 1 (Idempotency):

(a) a + a = a

(b) aa = a

- Theorem 2 (Null element):

(a) a + 1 = 1

(b) a0 = 0

- The<u>o</u>rem 3 (Involution)

*a* = *a*

- **Properties of 0 and 1 elements** (Table 2.1):

| OR               | AND            | Complement |

|------------------|----------------|------------|

| a + 0 = 0        | <i>a</i> 0 = 0 | 0' = 1     |

| <i>a</i> + 1 = 1 | a1 = a         | 1'=0       |

## Fundamentals of Boolean Algebra (3)

Theorem 4 (Absorption)

(a) a + ab = a

(b) a(a + b) = a

- Examples:

- (X + Y) + (X + Y)Z = X + Y- AB'(AB' + B'C) = AB'

- Theorem 5

(a) a + a'b = a + b

(b)

$$a(a' + b) = ab$$

- **Examples**:

- -B + AB'C'D = B + AC'D

- (X + Y)((X + Y)' + Z) = (X + Y)Z

## Fundamentals of Boolean Algebra (4)

• Theorem 6

(a) ab + ab' = a (b) (a + b)(a + b') = a

#### • Examples:

- ABC + AB'C = AC- (W' + X' + Y' + Z')(W' + X' + Y' + Z)(W' + X' + Y + Z')(W' + X' + Y + Z)= (W' + X' + Y')(W' + X' + Y + Z')(W' + X' + Y + Z)= (W' + X' + Y')(W' + X' + Y)= (W' + X' + Y')(W' + X' + Y)= (W' + X')

## Fundamentals of Boolean Algebra (5)

#### • Theorem 7

(a) ab + ab'c = ab + ac + c) = (a + b)(a + c)

#### • Examples:

-wy' + wx'y + wxyz + wxz' = wy' + wx'y + wxy + wxz'= wy' + wy + wxz'

= W

-(x'y'+z)(w+x'y'+z') = (x'y'+z)(w+x'y')

### Fundamentals of Boolean Algebra (6)

- Theorem 8 (DeMorgan's Theorem)

(a) (a + b)' = a'b'

(b) (ab)' = a' + b'

- Generalized DeMorgan's Theorem

(a) (a + b + ... z)' = a'b' ... z'

(b) (ab ... z)' = a' + b' + ... z'

- Examples: -(a+bc)' = (a+(bc))'

-

$$(a + bc)' = (a + (bc))$$

=  $a'(bc)'$

=  $a'(b' + c')$

=  $a'b' + a'c'$

Note:  $(a + bc)' \neq a'b' + c'$

# Logic Gates

#### • Electrical Signals and Logic Values

| Electric Signal  | Logic Value    |                |  |

|------------------|----------------|----------------|--|

|                  | Positive Logic | Negative Logic |  |

| High Voltage (H) | 1              | 0              |  |

| Low Voltage (L)  | 0              | 1              |  |

- A signal that is set to logic 1 is said to be asserted, active, or true.

- An *active-high* signal is asserted when it is high (positive logic).

- An active-low signal is asserted when it is low (negative logic).

# AND

– Logic notation A•B = C (Sometimes AB = C)

| Α | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

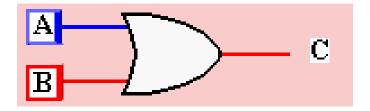

# OR

| Α | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

- Logic notation A + B = C

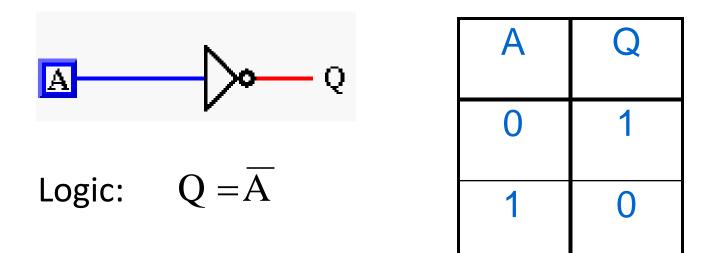

# Inversion (NOT)

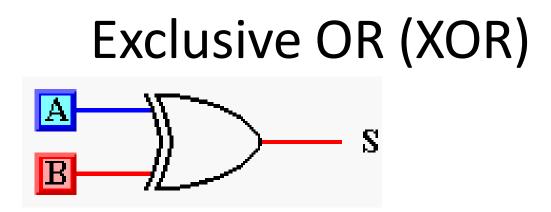

Either A or B, but not both

This is sometimes called the **inequality detector**, because the result will be 0 when the inputs are the same and 1 when they are different.

The truth table is the same as for S on Binary Addition.  $S = A \oplus B$

| Α | В | S |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

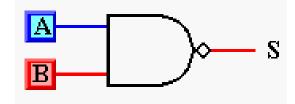

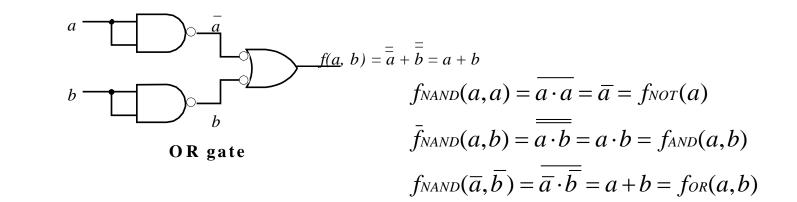

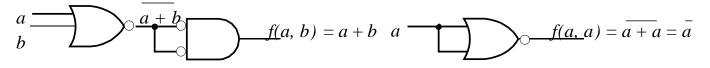

### **UNIVERSAL GATES**

# NAND (NOT AND)

| Α | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$Q = A \cdot B$

# **Basic Functional Components**

• AND, OR, and NOT gates constructed exclusively from NAND gates

$$a = b$$

$b = \overline{ab} = ab$   $a = \overline{a}$

AND gate

NOT gate

Hence, NAND gate may be used to implement all three elementary operators.

# NOR (NOT OR)

$$Q = A + B$$

| Α | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

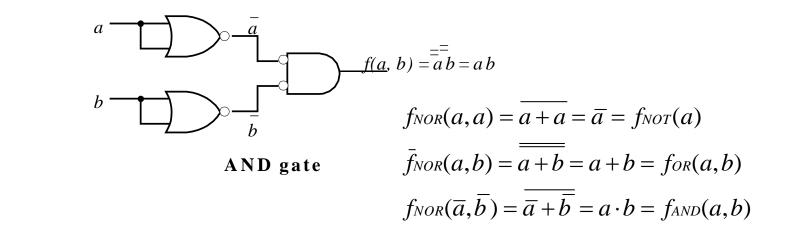

### **Basic Functional Components**

• AND, OR, and NOT gates constructed exclusively from NOR gates.

**OR** gate

NOT gate

Hence, NOR gate may be used to implement all three elementary operators.

### Summary

|     | Summary for all 2-input gates |                     |                          |   |   |   |   |

|-----|-------------------------------|---------------------|--------------------------|---|---|---|---|

| Inp | uts                           | Output of each gate |                          |   |   |   |   |

| A   | В                             | AND                 | AND NAND OR NOR XOR XNOR |   |   |   |   |

| 0   | 0                             | 0                   | 1                        | 0 | 1 | 0 | 1 |

| 0   | 1                             | 0                   | 1                        | 1 | 0 | 1 | 0 |

| 1   | 0                             | 0                   | 1                        | 1 | 0 | 1 | 0 |

| 1   | 1                             | 1                   | 0                        | 1 | 0 | 0 | 1 |

# MINIMIZATON OF LOGIC EXPRESSION

- Goal -- minimize the cost of realizing a switching function

- Cost measures and other considerations

- Number of gates

- Number of levels

- Gate fan in and/or fan out

- Interconnection complexity

- Preventing hazards

- Two-level realizations

- Minimize the number of gates (terms in switching function)

- Minimize the fan in (literals in switching function)

- Commonly used techniques

- Boolean algebra postulates and theorems

- Karnaugh maps

### Simplification Using Boolean Algebra

A simplified Boolean expression uses the fewest gates possible to implement a given expression.

### Simplification Using Boolean Algebra

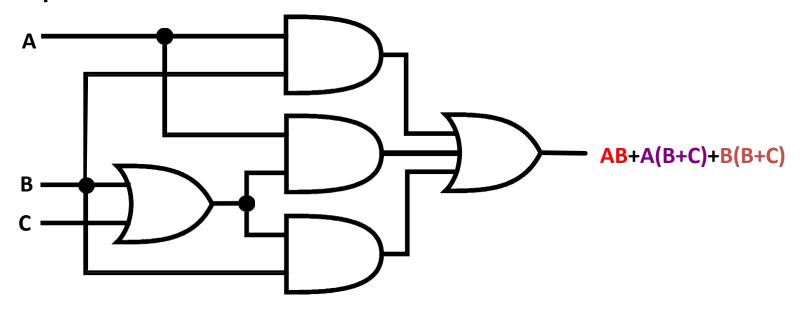

- AB+A(B+C)+B(B+C)

- (distributive law)

- AB+AB+AC+BB+BC

- (BB=B)

- AB+AB+AC+<mark>B</mark>+BC

- (AB+AB=AB)

- AB+AC+B+BC

- (B+BC=B)

- AB+AC+<mark>B</mark>

- (AB+B=B)

- **B**+AC

### Simplification Using Boolean Algebra

• Try these:

# $\begin{bmatrix} AB \ (\overline{C} + BD) + AB \ ]\overline{C} \\ AB\overline{C} + ABC + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} AB \\ + \overline{AC} + \overline{ABC} \ - - - \end{bmatrix}$

### Standard Forms of Boolean Expressions

- All Boolean expressions, regardless of their form, can be converted into either of two standard forms:

- The sum-of-products (SOP) form

- The product-of-sums (POS) form

- Standardization makes the evaluation, simplification, and implementation of Boolean expressions much more systematic and easier.

# The Sum-of-Products (SOP) Form

- An SOP expression

→ when two or

more product terms

are summed by

Boolean addition.

- Examples:

AB + ABC

ABC + CDE + BCD AB +

ABC + AC

– Also:

A + ABC + BCD

- In an SOP form, a single overbar cannot extend over more than one variable; however, more than one variable <u>in a term can have an</u> overbar:

- example:  $\overline{A}\overline{B}\overline{C}$  is OK!

**But not**: *ABC*

### **Converting Product Terms to Standard SOP**

• **Step 1:** Multiply each nonstandard product term by a term made up of the sum of a missing variable and its complement. This results in two product terms.

As you know, you can multiply anything by 1 without changing its value.

• Step 2: Repeat step 1 until all resulting product term contains all variables in the domain in either complemented or uncomplemented form. In converting a product term to standard form, the number of product terms is doubled for each missing variable.

# Converting Product Terms to Standard SOP (example)

• Convert the following Boolean expression into standard SOP form:

$ABC + \overline{AB} + \overline{ABCD}$

ABC = ABC(D+D) = ABCD + ABCD + ABCD + ABCD + ABC = AB(C+C) = ABC + ABC

$\overline{A}\overline{B}C(D+\overline{D}) + \overline{A}\overline{B}\overline{C}(D+\overline{D}) = \overline{\overline{A}\overline{B}CD} + \overline{A}\overline{B}\overline{C}\overline{D} + \overline{\overline{A}B}\overline{\overline{C}D} + \overline{\overline{A}B}\overline{\overline{C}D}$

$A\overline{B}C + \overline{A}\overline{B} + AB\overline{C}D = \overline{ABCD} + \overline{AB$

# The Product-of-Sums (POS) Form

When two or more sum terms are multiplied, the result expression is a product- of-sums (POS):

– Examples:

In a POS form, a single single overbar cannot extend over more than one variable; however, more than e variable in a term have an overbar: example: A + B + Cis OK! example: \_\_\_\_\_\_ is OK!

**But not:**  $\overline{A+B+C}$

### Converting a Sum Term to Standard POS

- **Step 1:** Add to each nonstandard product term a term made up of the product of the missing variable and its complement. This results in two sum terms.

- As you know, you can add 0 to anything without changing its value.

- Step 2: Apply rule  $\rightarrow$  A+BC=(A+B)(A+C).

- Step 3: Repeat step 1 until all resulting sum terms contain all variable in the domain in either complemented or uncomplemented form.

# Converting a Sum Term to Standard POS (example)

Convert the following Boolean expression into standard POS form:

$(A + \overline{B} + C)(\overline{B} + C + \overline{D})(A + \overline{B} + \overline{C} + D)$

$$A + \overline{B} + C = A + \overline{B} + C + D\overline{D} = (A + \overline{B} + C + D)(A + \overline{B} + C + D)$$

D)

B + C + D = B + C + D + AA = (A + B + C + D)(A + B + C + C)

### **Boolean Expressions & Truth Tables**

- All <u>standard Boolean expression</u> can be easily converted into truth table format using binary values for each term in the expression.

- Also, <u>standard SOP or POS</u> expression can be determined from the truth table.

### Converting SOP Expressions to Truth Table Format

- Recall the fact:

- An SOP expression is equal to 1 only if at least one of the product term is equal to 1.

- Constructing a truth table:

- Step 1: List all possible combinations of binary values of the variables in the expression.

– Step 2: Convert the SOP expression to standard form if it is not already.

Step 3: Place a 1 in the output column (X) for each binary value that makes the <u>standard SOP</u> expression a 1 and place 0 for all the remaining binary values.

### Converting SOP Expressions to Truth Table Format (example)

Develop a truth table for the standard SOP expression

$ABC + ABC + \overline{ABC}$

| In | Inputs<br>Inputs |      | Output | Product                                |

|----|------------------|------|--------|----------------------------------------|

| Å  | nВ               | ധ    | X      | Term                                   |

| θ  | 0                | в    | 0      |                                        |

| θ  | 0                | -41  |        | $\overline{A}\overline{B}\overline{C}$ |

| δ  | ∽च⊢              | 8    | 0      |                                        |

| δ  | ∽च⊢              | ⊷∓   | 0      |                                        |

| 4  | 0                | 8    | ╌┩┥    | $A\overline{B}\overline{C}$            |

| 1  | 0                | ∽न्न | 0      |                                        |

| 1  | 1                | θ    | 0      |                                        |

| 1  | ╌┩┥              | حطا  | 1      | ABC                                    |

### Converting POS Expressions to Truth Table Format

- Recall the fact:

- A POS expression is equal to 0 only if at least one of the product term is equal to 0.

- Constructing a truth table:

- Step 1: List all possible combinations of binary values of the variables in the expression.

Step 2: Convert the POS expression to standard form if it is not already.

Step 3: Place a 0 in the output column (X) for each binary value that makes the <u>standard POS</u> expression a 0 and place 1 for all the remaining binary values.

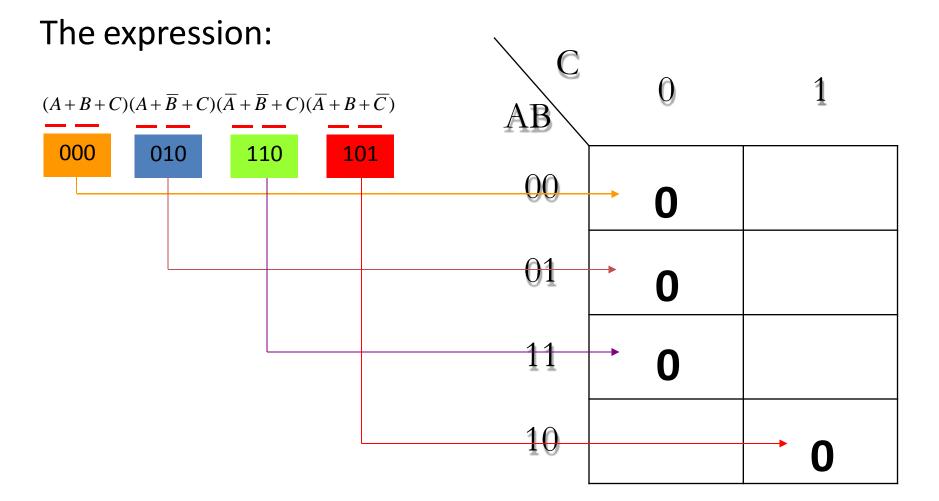

### Converting POS Expressions to Truth Table Format (example)

Develop a truth table for the standard SOP expression

$$(A + B + C)(A + B + C)(A + B + C)$$

$(A + B + C)(A + B + C)$

| Inputs |    | Output | Proluct |             |

|--------|----|--------|---------|-------------|

| A      | BB | S      | X       | <b>Term</b> |

| 0      | 0  | 0      | 0       | (A+B+C)     |

| 0      | Ø  | 1      | 1       | _           |

| 0      | 1  | 0      | 0       | (A+B+C)     |

| 0      | 1  | 1      | 0       | (A+B+C)     |

| 1      | 0  | 0      | 1       |             |

| 1      | 0  | 1      | 0       | (A+B+C)     |

| 1      | 1  | 0      | 0       | (A+B+C)     |

| 1      | 1  | 1      | 1       |             |

### Determining Standard Expression from a Truth Table

- To determine the standard **SOP expression** represented by a truth table.

- Instructions:

- Step 1: List the binary values of the input variables for which the output is 1.

- Step 2: Convert each binary value to the corresponding product term by replacing:

- each 1 with the corresponding variable, and

- each 0 with the corresponding variable complement.

- Example: 1010  $\rightarrow A\overline{B}C\overline{D}$

### Determining Standard Expression from a Truth Table

- To determine the standard **POS expression** represented by a truth table.

- Instructions:

- Step 1: List the binary values of the input variables for which the output is 0.

- Step 2: Convert each binary value to the corresponding product term by replacing:

- each 1 with the corresponding variable complement, and

- each 0 with the corresponding variable.

- Example: 1001  $\rightarrow \overline{A} + B + C + \overline{D}$

# The Karnaugh Map

- Feel a little difficult using Boolean algebra laws, rules, and theorems to simplify logic?

- A K-map provides a systematic method for simplifying Boolean expressions and, if properly used, will produce the simplest SOP or POS expression possible, known as the <u>minimum expression</u>.

# What is K-Map

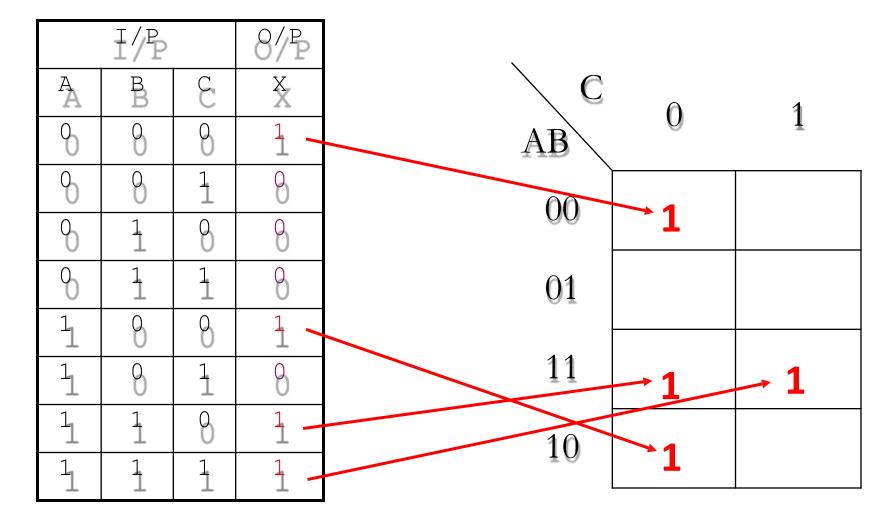

- It's similar to truth table; instead of being organized (i/p and o/p) into columns and rows, the K-map is an array of cells in which each cell represents a binary value of the input variables.

- The cells are arranged in a way so that simplification of a given expression is simply a matter of properly grouping the cells.

- K-maps can be used for expressions with 2, 3, 4, and 5 variables.

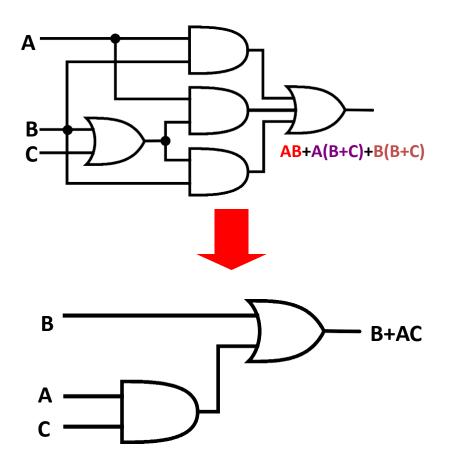

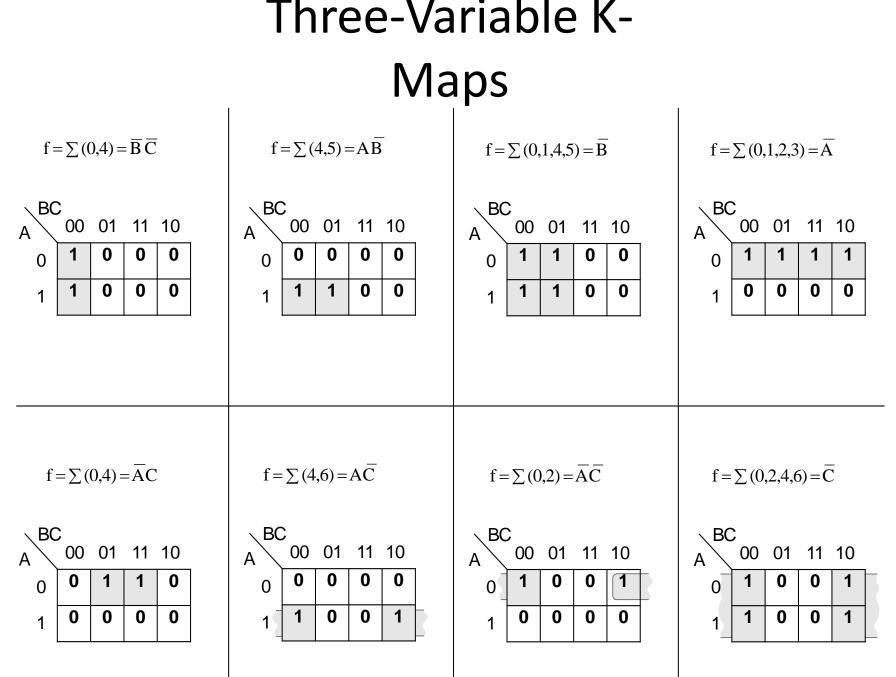

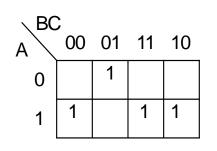

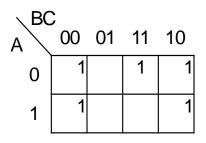

# The 3 Variable K-Map

• There are 8 cells as shown:

105

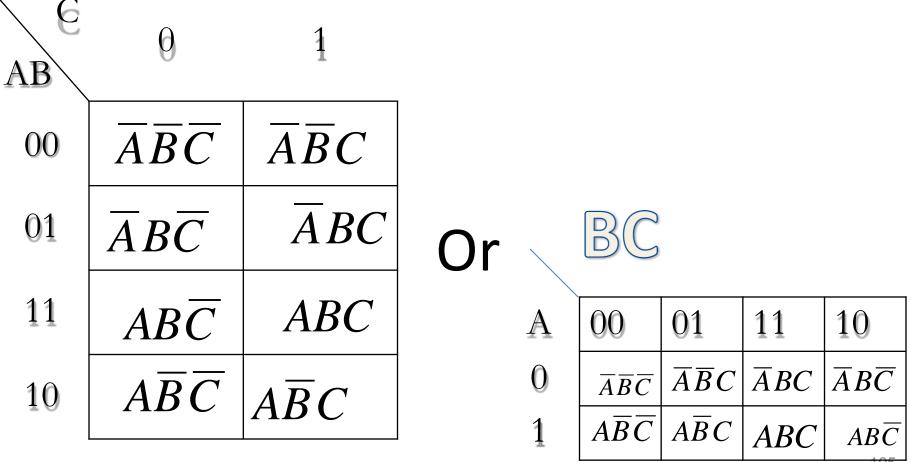

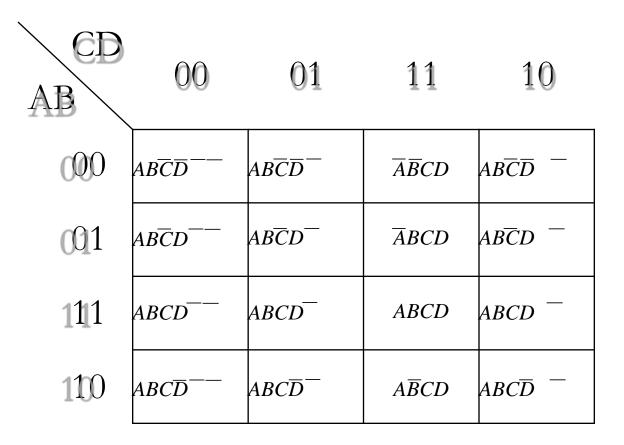

### The 4-Variable K-Map

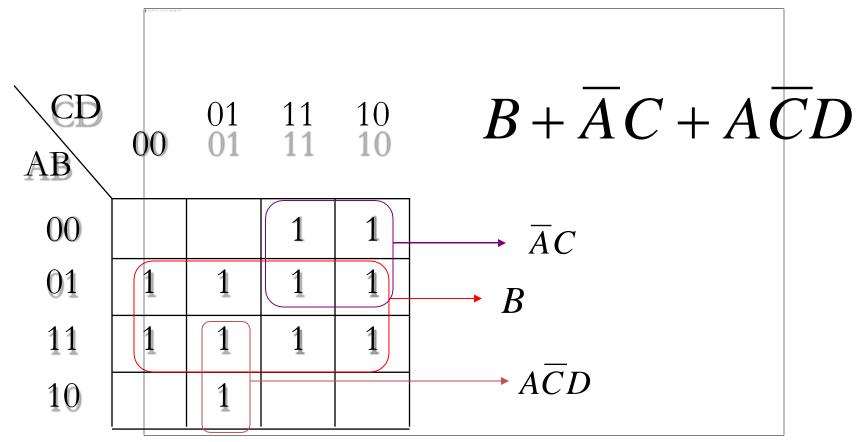

# **K-Map SOP Minimization**

- The K-Map is used for simplifying Boolean expressions to their minimal form.

- A minimized SOP expression contains the fewest possible terms with fewest possible variables per term.

- Generally, a minimum SOP expression can be implemented with fewer logic gates than a standard expression.

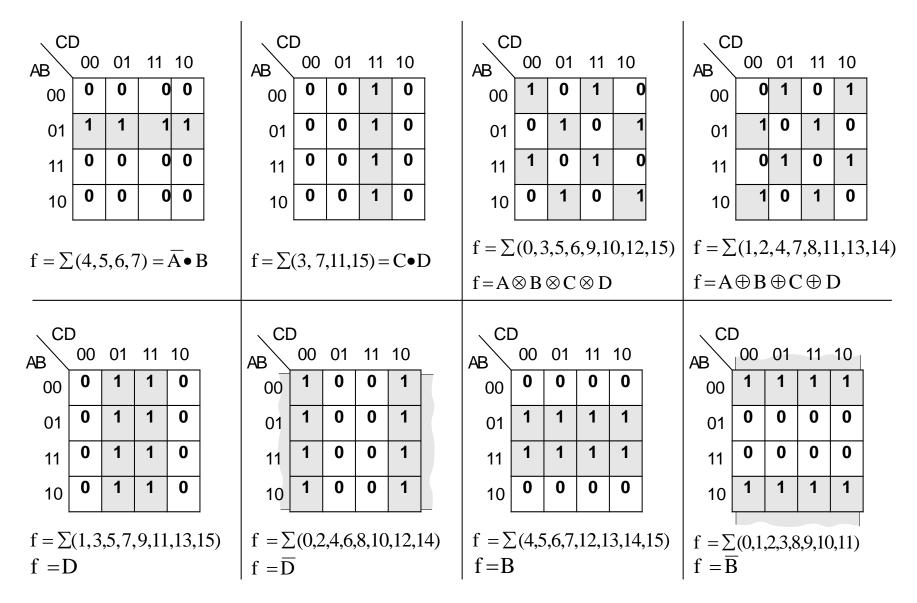

# Karnaugh Maps (K-maps)

If m<sub>i</sub> is a minterm of f, then place a 1 in cell i of the K-map.

- If  $M_i$  is a maxterm of f, then place a 0 in cell i.

- If d<sub>i</sub> is a don't care of f, then place a d or x in cell i.

#### Examples

• Two variable K-map  $f(A,B)=\sum m(0,1,3)=A^B^+A^B+AB$ 0 1 B 0 0 1

# Grouping the 1s (rules)

- 1. A group must contain either 1,2,4,8,or 16 cells (depending on number of variables in the expression)

- 2. Each cell in a group must be adjacent to one or more cells in that same group, but all cells in the group do not have to be adjacent to each other.

- 3. Always include the largest possible number of 1s in a group in accordance with rule 1.

- 4. Each 1 on the map must be included in at least one group. The 1s already in a group can be included in another group as long as the overlapping groups include noncommon 1s.

#### Determining the Minimum SOP Expression from the Map

- 2. Determine the minimum product term for each group.

- For a 3-variable map:

- 1. A 1-cell group yields a 3-variable product term

- 2. A 2-cell group yields a 2-variable product term

- 3. A 4-cell group yields a 1-variable product term

- 4. An 8-cell group yields a value of 1 for the expression.

- For a 4-variable map:

- 1. A 1-cell group yields a 4-variable product term

- 2. A 2-cell group yields a 3-variable product term

- 3. A 4-cell group yields a 2-variable product term

- 4. An 8-cell group yields a a 1-variable product term

- 5. A 16-cell group yields a value of 1 for the expression.

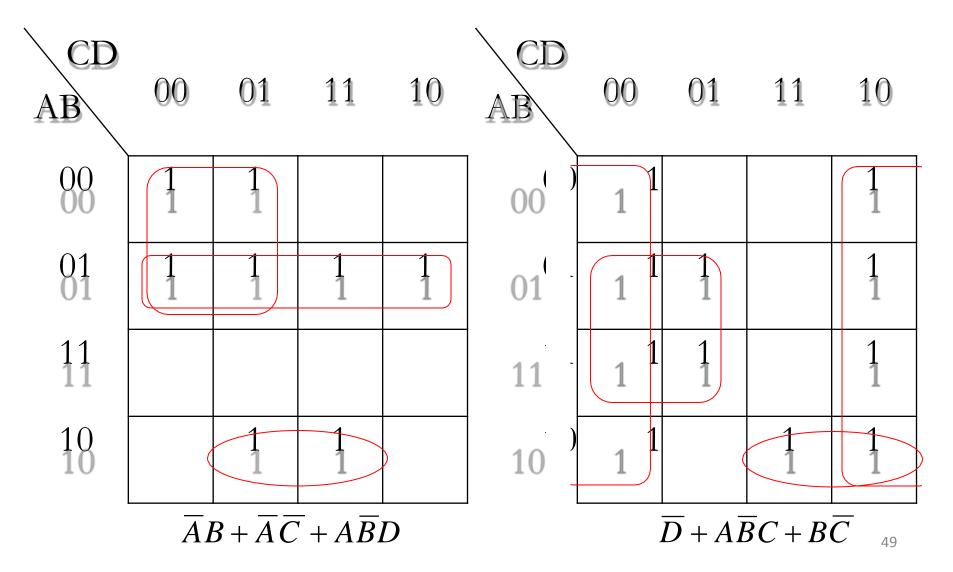

#### Determining the Minimum SOP Expression from the Map (example)

• We can write any way dither Alariable KrlAlage Examples

#### Determining the Minimum SOP Expression from the Map (exercises)

#### Four-Variable K-Maps

# Practicing K-Map (SOP)

#### $A\overline{B}C + \overline{A}BC + \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C}$

$\overline{B} + \overline{A}C$

# $\overline{B}\overline{C}\overline{D} + \overline{A}B\overline{C}\overline{D} + AB\overline{C}\overline{D} + \overline{A}\overline{B}CD + A\overline{B}CD + A\overline{B}CD + A\overline{B}C\overline{D} + \overline{A}BC\overline{D} + ABC\overline{D} + A\overline{B}C\overline{D}$

## Mapping Directly from a Truth Table

# "Don't Care" Conditions

- Sometimes a situation arises in which some input variable combinations are not allowed, i.e. BCD code:

- There are six invalid combinations: 1010, 1011, 1100, 1101, 1110, and 1111.

- Since these unallowed states will never occur in an application involving the BCD code → they can be treated as "don't care" terms with respect to their effect on the output.

- The "don't care" terms can be used to advantage on the K-map (how? see the next slide).

# "Don't Care" Conditions

|     |             | AB                  | $\setminus \mathbf{CP}$ |     |   |     |     |   |

|-----|-------------|---------------------|-------------------------|-----|---|-----|-----|---|

| 11  | 01          | $\frac{1}{00}$      |                         | O/P |   | UTS | INP |   |

| 11  | 01          | 00                  |                         | Y   | D | С   | В   | A |

|     |             |                     | ABO                     | 0   | 8 | 0   | 8   | 8 |

|     |             |                     | 01                      | 0   | 1 | 0   | 0   | 0 |

|     |             |                     | U                       | 0   | 8 | 1   | 8   | 8 |

|     | •7          | •                   | 44                      | 0   | 1 | 1   | 0   | 0 |

|     | X           | X                   | U I                     | 0   | 8 | 8   | 1   | 8 |

|     | <b>N</b> .7 | X                   | 11                      | 0   | 1 | 0   | 1   | 0 |

| X   | X           | X                   |                         | 0   | 8 | 1   | 1   | 8 |

| X   | $1_{1}$     | <b>1</b> 1          | 10                      | 1   | 1 | 1   | 1   | 0 |

| A   |             |                     | 10                      | 1   | 8 | 8   | 8   | 1 |

|     |             |                     |                         | 1   | 1 | 0   | 0   | 1 |

|     |             | t "d <u>on'</u> t o |                         | x   | 0 | 1   | 8   | 1 |

|     | ABCD        | ABC +               | Y =                     | x   | 1 | 1   | 0   | 1 |

|     |             |                     |                         | x   | 0 | 8   | 1   | 1 |

|     | h "don't    | Wit                 |                         | x   | 1 | 0   | 1   | 1 |

| 3CD | Y = A + A   |                     |                         | x   | 8 | 1   | 1   | 1 |

|     |             |                     |                         | x   | 1 | 1   | 1   | 1 |

10

Х

Х

# Mapping a Standard POS Expression (full example)

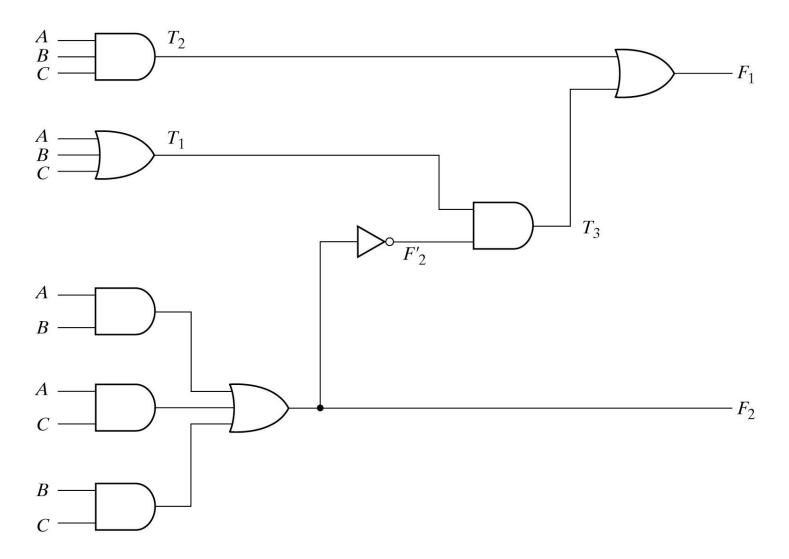

# **Combinational Circuits**

Fig. 4-1 Block Diagram of Combinational Circuit

Fig. 4-2 Logic Diagram for Analysis Example

# **Designing Combinational Circuits**

In general we have to do following steps:

- 1. Problem description

- 2. Input/output of the circuit

- 3. Define truth table

- 4. Simplification for each output

- 5. Draw the circuit

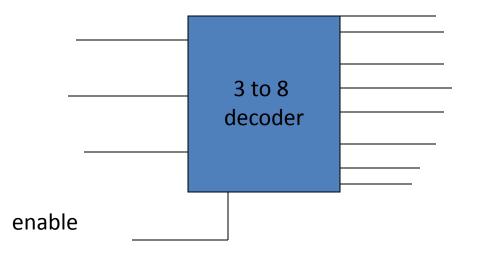

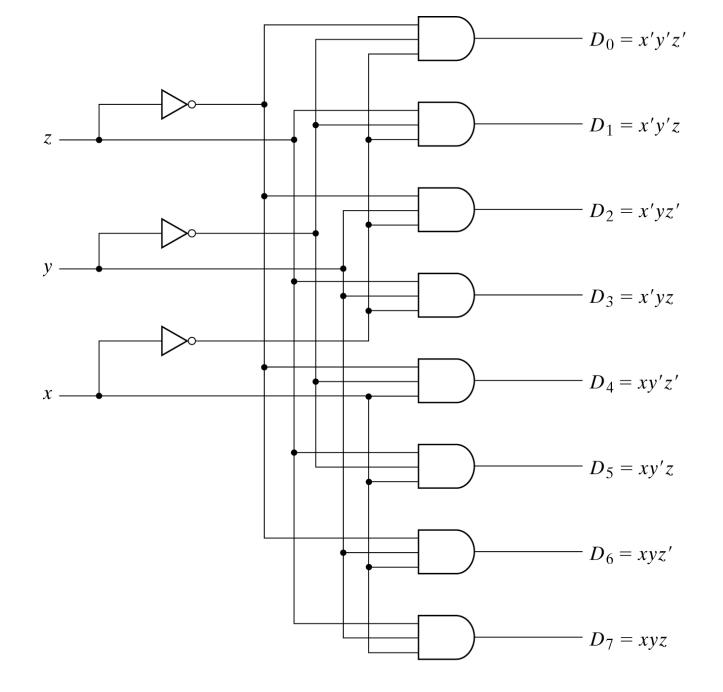

# Decoder

Is a combinational circuit that converts binary information from n input lines to a maximum of 2<sup>n</sup> unique output lines For example if the number of input is n=3 the number of output lines can be m=2<sup>3</sup>. It is also known as 1 of 8 because one output line is selected out of 8 available lines:

Fig. 4-18 3-to-8-Line Decoder

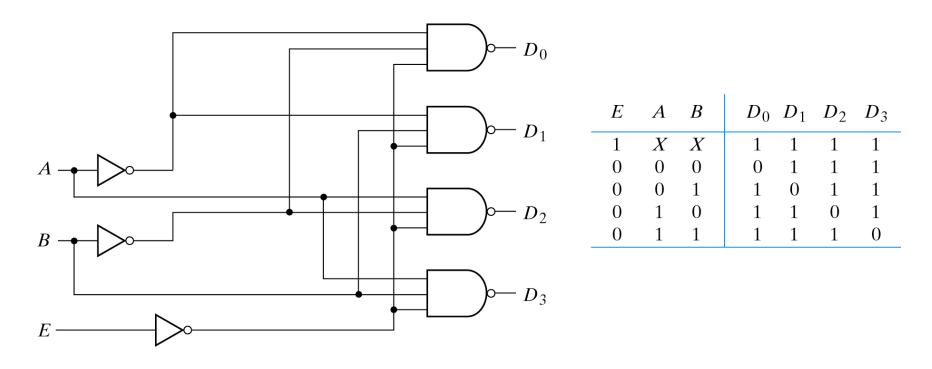

# **Decoder with Enable Line**

- Decoders usually have an enable line,

- If enable=0 , decoder is off. It means all output lines are zero

- If enable=1, decoder is on and depending on input, the corresponding output line is 1, all other lines are 0

- See the truth table in next slide

# Truth table for decoder

E a2 a1 a0 D7 D6 D5 D4 D3 D2 D1 D0

\_\_\_\_\_

| 0 | Х | Х    | Х | 0               | 0               | 0    | 0    | 0     | 0   | 0 | 0 |

|---|---|------|---|-----------------|-----------------|------|------|-------|-----|---|---|

| 1 | 0 | 0    | 0 | 0               | 0               | 0    | 0    | 0     | 0   | 0 | 1 |

| 1 | 0 | 0    | 1 | 0               | 0               | 0    | 0    | 0     | 0   | 1 | 0 |

| 1 |   |      |   |                 |                 |      |      |       |     |   |   |

| 1 |   | •••• |   | • • • • • • • • | •••••           | •••• |      |       | ••• |   |   |

| 1 |   | •••• |   | •••••           | • • • • • • • • | •••• | •••• | ••••• | ••  |   |   |

| 1 |   |      |   |                 |                 |      |      |       |     |   |   |

| 1 |   |      |   |                 |                 |      |      |       |     |   |   |

| 1 | 1 | 1    | 1 | 1 (             | 0               | 0    | 0    | 0     | 0   | 0 | 0 |

(a) Logic diagram

(b) Truth table

Fig. 4-19 2-to-4-Line Decoder with Enable Input

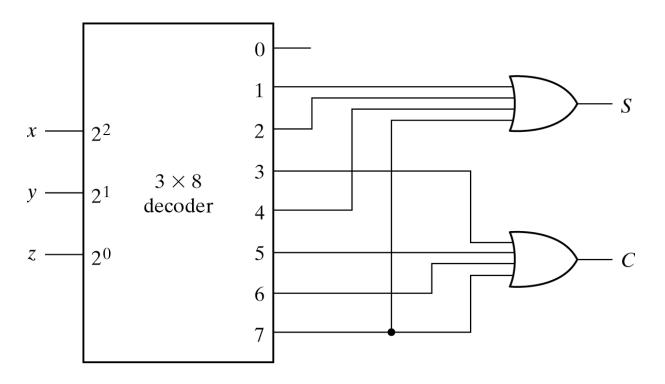

## Major application of Decoder

• Decoder is use to implement any combinational cicuits ( $f^n$ ) For example the truth table for full adder is s (x,y,z) =  $\sum (1,2,4,7)$ and C(x,y,z)=  $\sum (3,5,6,7)$ . The implementation with decoder is:

Fig. 4-21 Implementation of a Full Adder with a Decoder

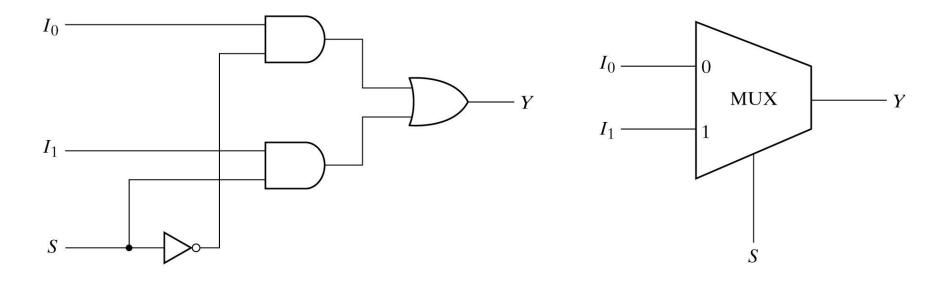

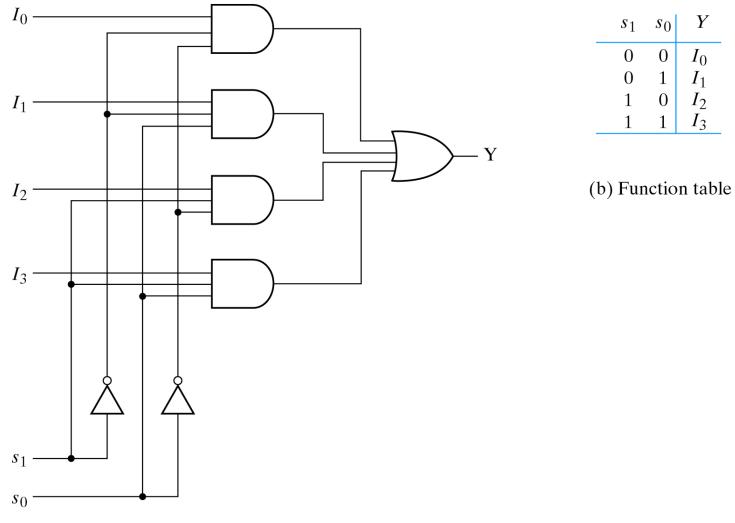

# Multiplexer

- It is a combinational circuit that selects binary information from one of the input lines and directs it to a single output line

- Usually there are 2<sup>n</sup> input lines and n selection lines whose bit combinations determine which input line is selected

- For example for 2-to-1 multiplexer if selection S is zero then I<sub>0</sub> has the path to output and if S is one I<sub>1</sub> has the path to output (see the next slide)

# 2-to-1 multiplexer

(a) Logic diagram

(b) Block diagram

(a) Logic diagram

Fig. 4-25 4-to-1-Line Multiplexer

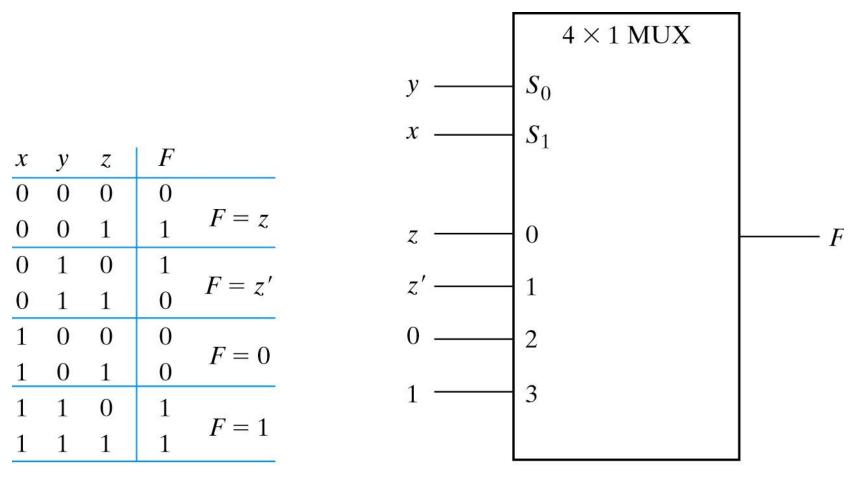

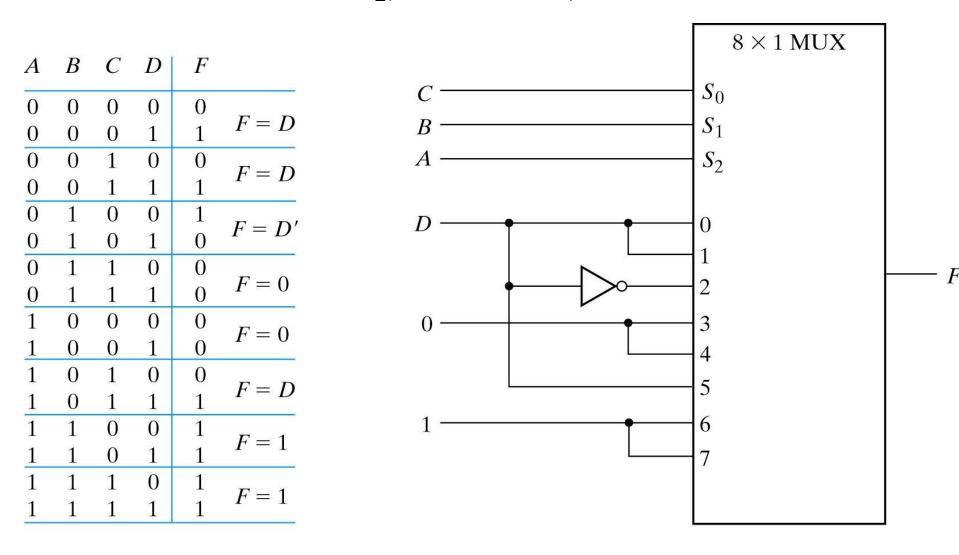

## **Boolean function Implementation**

- Another method for implementing boolean function is using multiplexer

- For doing that assume boolean function has n variables. We have to use multiplexer with n-1 selection lines and

- 1- first n-1 variables of function is used for data input

- 2- the remaining single variable (named z) is used for data input. Each data input can be z, z', 1 or 0. From truth table we have to find the relation of F and z to be able to design input lines. For example :  $f(x,y,z) = \sum (1,2,6,7)$

(a) Truth table

(b) Multiplexer implementation

Fig. 4-27 Implementing a Boolean Function with a Multiplexer

$FA,B,C,D = \sum (1,3,4,11,12,13,14,15)$

Fig. 4-28 Implementing a 4-Input Function with a Multiplexer

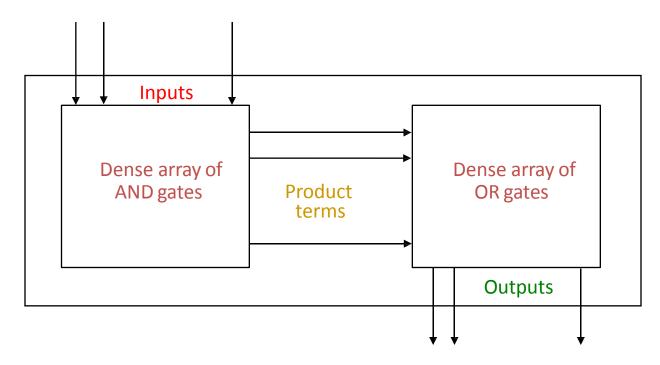

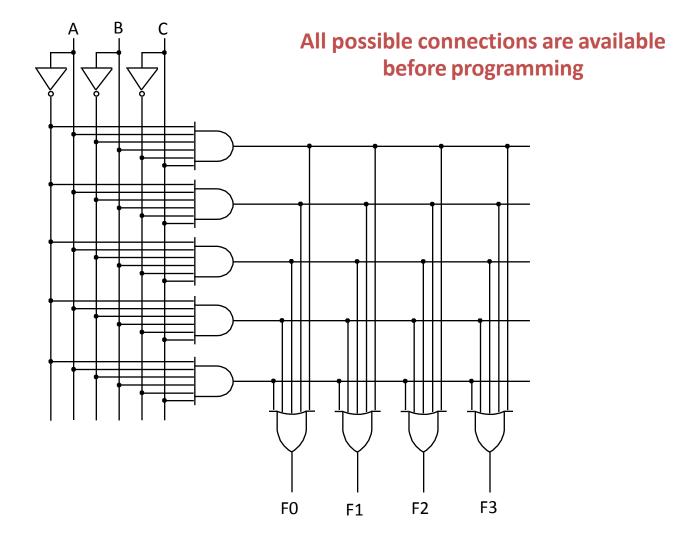

# Prgrammable Logic Organization

- Pre-fabricated building block of many AND/OR gates (or NOR, NAND)

- "Personalized" by making or breaking connections among the gates

Programmable Array Block Diagram for Sum of ProductsForm

# Basic Programmable Logic

Organizations

Depending on which of the AND/OR logic arrays is programmable, we have three basic organizations

| ORGANIZATION | ANDARRAY | ORARRAY |

|--------------|----------|---------|

| PAL          | PROG.    | FIXED   |

| PROM         | FIXED    | PROG.   |

| PLA          | PROG.    | PROG.   |

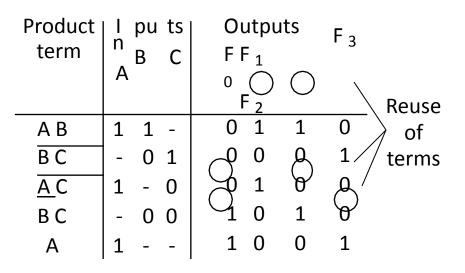

## **PLA Logic Implementation**

Key to Success: Shared Product Terms

#### **Equations**

Example:

$F0 = A + \underline{B}C$   $F1 = A \underline{C} + A B$   $F2 = B \underline{C} + A B$ F3 = B C + A

#### **Personality Matrix**

#### Input Side:

- 1 = asserted in term

- 0 = negated in term

- = does not participate

#### **Output Side:**

1 = term connected to output 0 = no connection to output

## **PLA Logic Implementation**

#### Example Continued - Unprogrammed device

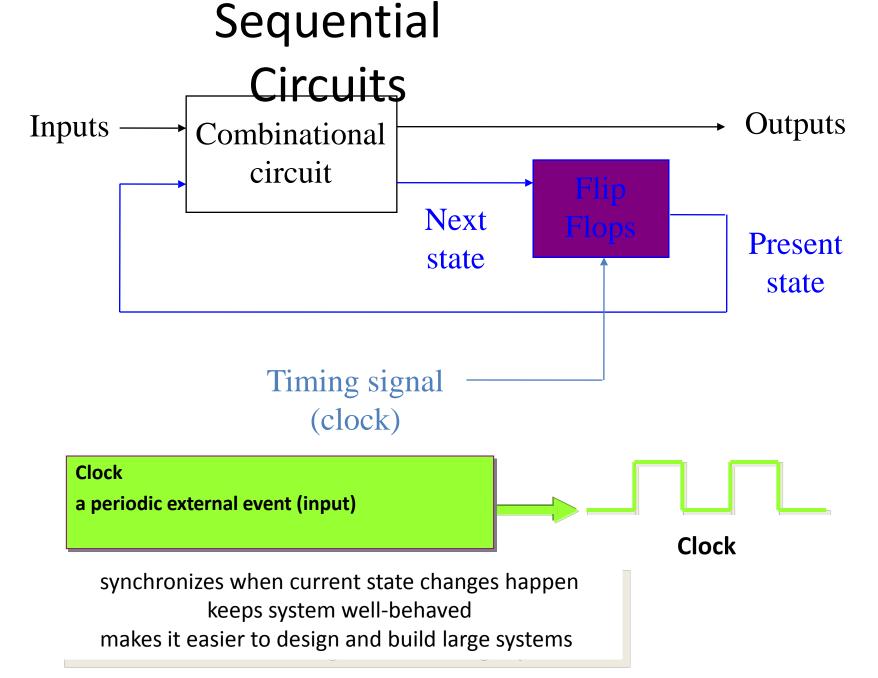

### **Sequential Circuits**

- Circuits require memory to store intermediate data

- Sequential circuits use a periodic signal to determine when to store values.

- A clock signal can determine storage times

- Clock signals are periodic

- Single bit storage element is a flip flop

- A basic type of flip flop is a latch

- Latches are made from logic gates

- NAND, NOR, AND, OR, Inverter

#### The story so far

- Logical operations which respond to **combinations** of inputs to produce an output.

- Call these **combinational logic** circuits.

- For example, can add two numbers. But:

- No way of adding two numbers, then adding a third (a sequential operation);

- No way of remembering or storing information after inputs have been removed.

- To handle this, we need **sequential logic** capable of storing intermediate (and final) results.

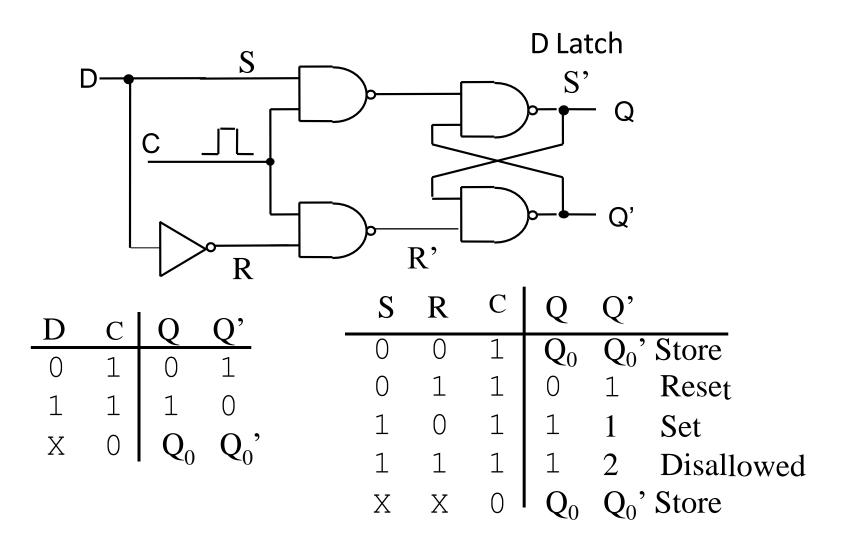

## Sequential Circuits: Flip flops

# Overview

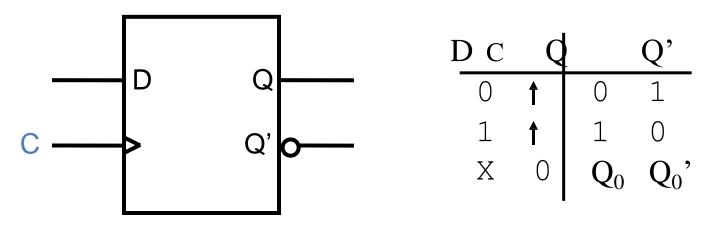

• Latches respond to trigger levels on control inputs

– Example: If G = 1, input reflected at output

- Difficult to precisely time when to store data with latches

- Flip flips store data on a rising or falling trigger edge.

- Example: control input transitions from 0 -> 1, data input appears at output

- Data remains stable in the flip flop until until next rising edge.

- Different types of flip flops serve different functions

- Flip flops can be defined with characteristic functions.

• When C is high, D passes from input to output (Q)

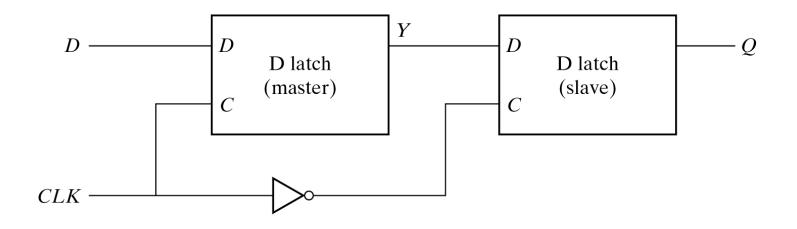

#### Master-Slave D Flip Flop

- Consider two latches combined together

- Only one *C* value active at a time

- Output changes on falling edge of the clock

Fig. 5-9 Master-Slave D Flip-Flop

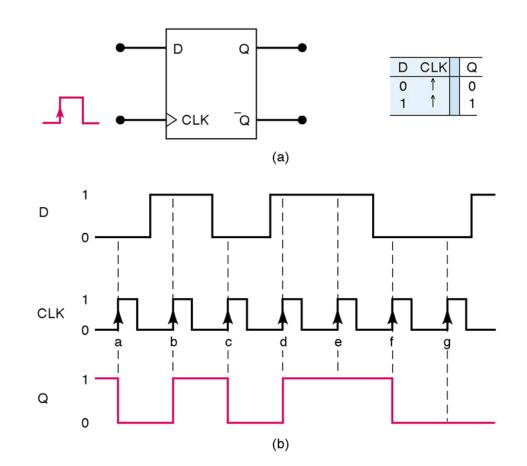

- Stores a value on the positive edge of C<sup>D</sup> Flip-Flop

- Input changes at other times have no effect on output

Positive edge triggered

D gets latched to Q on the rising edge of the clock.

Clocked D Flip-Flop

- Stores a value on the positive edge of *C*

- Input changes at other times have no effect on output

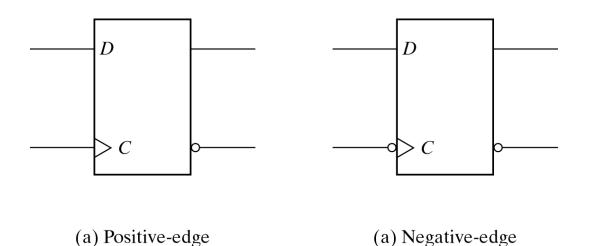

Positive and Negative Edge D Flip-Flop

- D flops can be triggered on positive or negative edge

- Bubble before *Clock (C)* input indicates negative edge trigger

Fig. 5-11 Graphic Symbol for Edge-Triggered D Flip-Flop

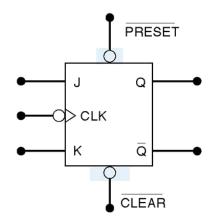

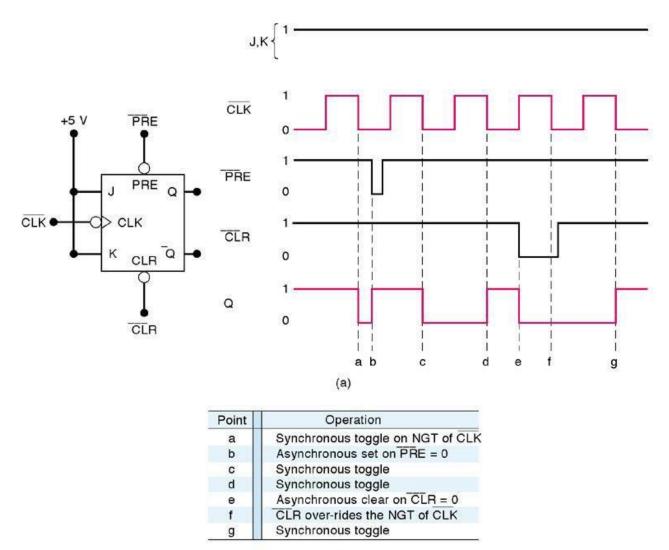

Asynchronous Inputs

• J, K are synchronous inputs

o Effects on the output are synchronized with the CLK input.

• **Asynchronous inputs** operate independently of the synchronous inputs and clock

o Set the FF to 1/0 states at any time.

| PRESET | CLEAR | FF response               |

|--------|-------|---------------------------|

| 1      | 1     | Clocked operation*        |

| 0      | 1     | Q = 1 (regardless of CLK) |

| 1      | 0     | Q = 0 (regardless of CLK) |

| 0      | 0     | Not used                  |

\*Q will respond to J, K, and CLK

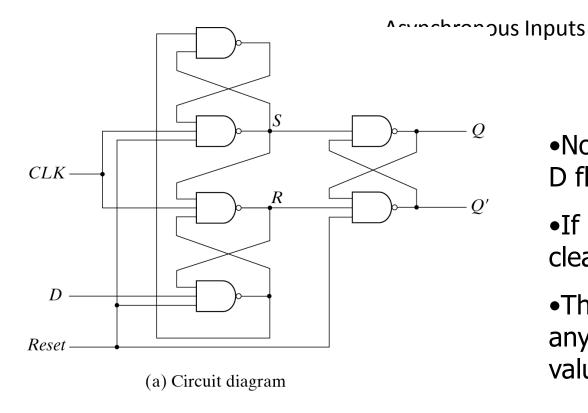

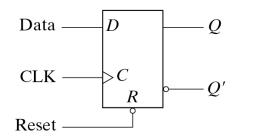

#### Asynchronous Inputs

(b) Graphic symbol

| R | С          | D      | Q | Q' |

|---|------------|--------|---|----|

| 0 | Х          | X<br>0 | 0 | 1  |

| 1 | $\uparrow$ | 0      | 0 | 1  |

| 1 | $\uparrow$ | 1      | 1 | 0  |

(b) Function table

•Note reset signal (R) for D flip flop

•If R = 0, the output Q is cleared

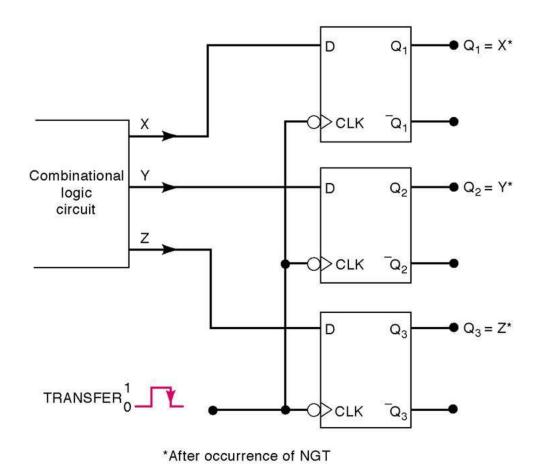

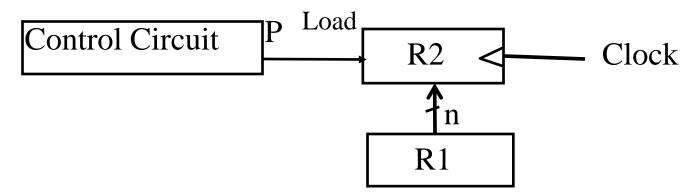

•This event can occur at any time, regardless of the value of the CLK Parallel Data Transfer

- Flip flops store outputs from combinational logic

- Multiple flops can store a collection of data

# Summary

- Flip flops are powerful storage elements

- They can be constructed from gates and latches!

- D flip flop is simplest and most widely used

- Asynchronous inputs allow for clearing and presetting the flip flop output

- Multiple flops allow for data storage

- The basis of computer memory!

- Combine storage and logic to make a computation circuit

- Next time: Analyzing sequential circuits.

# Counters

- Counters are important components in computers

- The increment or decrement by one in response to input

- Two main types of counters

- Ripple (asynchronous) counters

- Synchronous counters

- Ripple counters

- Flip flop output serves as a source for triggering other flip flops

- Synchronous counters

- All flip flops triggered by a clock signal

- Synchronous counters are more widely used in industry.

#### Counters

- •Counter: A register that goes through a prescribed series of states

- •Binary counter

- Counter that follows a binary sequence

- N bit binary counter counts in binary from n to 2<sup>n-1</sup>

- •Ripple counters triggered by initial Count signal

- •Applications:

- Watches

- Clocks

- Alarms

- Web browser refresh

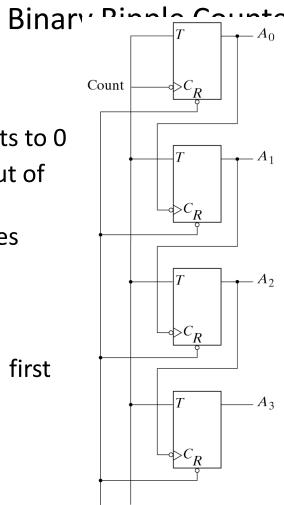

Logic-1

(a) With T flip-flops

Reset

Reset

Fig. 6-8 4-Bit Binary Ripple Counter

- Reset signal sets all outputs to 0

- Count signal toggles output of low-order flip flop

- Low-order flip flop provides trigger for adjacent flip flop

- Not all flops change value simultaneously

- Lower-order flops change first

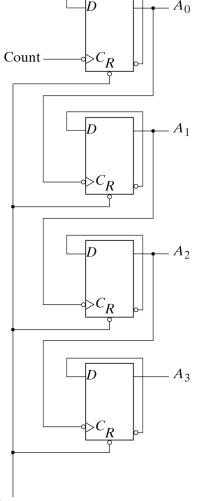

- Focus on D flip flop implementation

#### Asynchronous Counters

- Each FF output drives the CLK input of the next FF.

- FFs do not change states in exact synchronism with the applied clock pulses.

- There is delay between the responses of successive FFs.

- *Ripple counter* due to the way the FFs respond one after another in a kind of rippling effect.

| A <sub>3</sub> | <b>A</b> <sub>2</sub> | <b>A</b> <sub>1</sub> | $\mathbf{A}_{0}$ |

|----------------|-----------------------|-----------------------|------------------|

| 0              | 0                     | 0                     | 0                |

| 0              | 0                     | 0                     | 1                |

| 0              | 0                     | 1                     | 0                |

| 0              | 0                     | 1                     | 1                |

| 0              | 1                     | 0                     | 0                |

| 0              | 1                     | 0                     | 1                |

| 1              | 0                     | 0                     | 0                |

| 1              | 0                     | 0                     | _1               |

#### Synchrono

- Synchronous(parallel) counters

- All of the FFs are triggered simultaneously by the clock input pulses.

- All FFs change at same time

- Remember

- If J=K=O, flop maintains value

- If J=K=1, flop toggles

- Most counters are synchronous in computer systems.

- Can also be made from D flops

- Value increments on positive edge

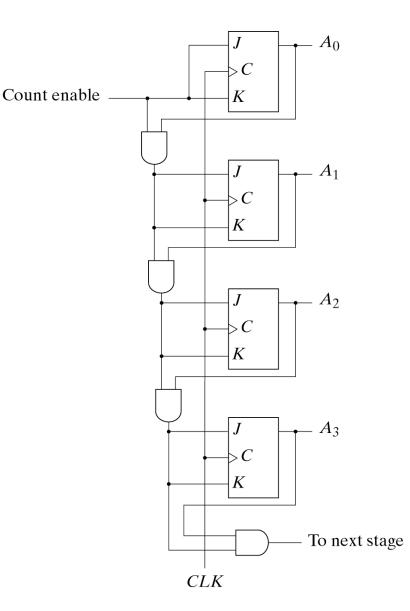

Fig. 6-12 4-Bit Synchronous Binary Counter

#### Synchronous counters

- Synchronous counters

- Same counter as previous slide except Count enable replaced by J=K=1

- Note that clock signal is a square wave

- Clock fans out to all clock inputs

Circuit operation

| Count   | D   | C    | D     | A    |

|---------|-----|------|-------|------|

| 0       | 0   | 0    | 0     | D    |

| 1       | 0   | 0    | 0     | 1    |

| 2       | 0   | 0    | 1     | 0    |

| 3       | 0   | 0    | 1     | 1    |

|         | 0   | 1    | 0     | 0    |

| 5       | 0   | 1    | 0     | 1    |

| 4 5 6 7 | 0   | 1    | 1     | 0    |

| 7       | 0   | 1    | 1     | 1    |

| 8       | 1   | 0    | ò     | 0    |

| 9       | 1   | 0000 | 0     | 1    |

| 10      | 1   | 0    | 1     | D    |

| 11      | 1   | 0    | 1     | 1    |

| 12      | 1   | 1    | 0     | 0    |

| 13      | 1   | 1    | 0     | 1    |

| 14      | 1   | 1    | 1     | 0    |

| 15      | 1   | 1    | 1     | 1    |

| 0       | 0   | 0    | 0     | 0    |

| 12.42   |     | 1.0  | 417   | 274  |

| 10      | 357 | 325  |       | 335  |

| - C2    | 1.2 | etc. | - 223 | 1.14 |

- Count value increments on each negative edge

- Note that low-order bit (A) toggles on each clock cycle

# Registers

- Register

- Consists of N Flip-Flops

- Stores N bits

- Common clock used for all Flip-Flops

- Shift Register

- A register that provides the ability to shift its contents (either left or right).

- Must use Flip-Flops

- Either edge-triggered or master-slave

- Cannot use Level-sensitive Gated Latches

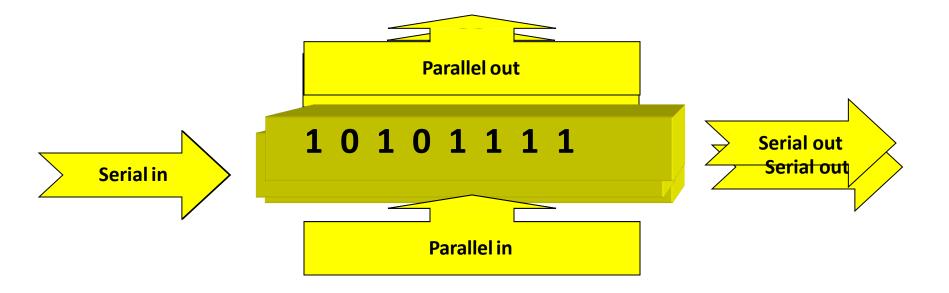

## **Overview of Shift Registers**

- A shift register is a sequential logic device made up of flip-flops that allows parallel or serial loading and serial or parallel outputs as well as shifting bit by bit.

- Common tasks of shift registers:

- Serial/parallel data conversion

- Time delay

- Ring counter

- Twisted-ring counter or Johnson counter

- Memory device

# **Characteristics of Shift Registers**

- Number of bits (4-bit, 8-bit, etc.)

- Loading

- Serial

- Parallel (asynchronous or synchronous)

- Common modes of operation.

- Parallel load

- Shift right-serial load

- Shift left-serial load

- Hold

- Clear

- Recirculating or non-recirculating

# Serial/Parallel Data Conversion

### Shift registers can be used to convert from serialto-parallel or the reverse from parallel-to-serial.

# UNIT-III

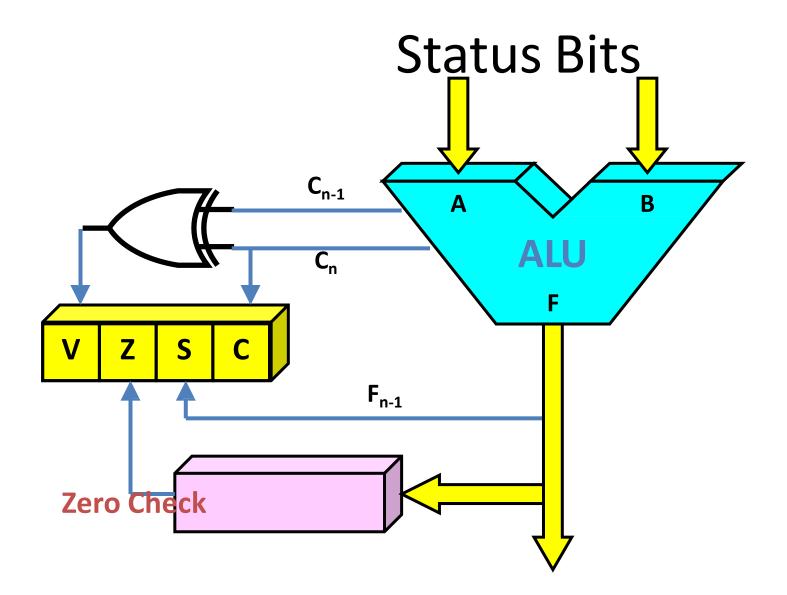

### **Computer Arithmetic**

• The Basic arithmetic operations are:

1. Addition 2. subtraction 3. Multiplication 4. Division.

- An arithmetic instruction may specify binary or decimal data, and in each case the data may be in fixed point or floating point.

- The solution to any problem that is stated by a finite number of well defined procedural steps is called an Algorithm.

- Here the arithmetic operation are implemented for the following data types:

- 1) Fixed point binary data in SMR

- 2) Fixed point binary data in S2's CR

- 3) Floating point binary data

- 4) Binary-coded decimal(BCD)

• There are three ways to represent negative fixed point binary numbers.

1)SMR 2)Signed 1'S Comp 3)Signed 2's Comp

• Floating point operations most of the computers use signed magnitude representation for the mantissa.

## Addition Algorithm

- when the signs of A and B are identical add the two magnitudes and attach the sign of A to the result.

- When the signs of A and B are different compare the magnitudes and subtract the smaller number from the larger. Choose the sign of the result to be the same as A if A>B or the complement of the sign of A if A<B .if the two magnitudes are equal subtract b from a and make the sign of the result positive.

| Operation | Add Magnitudes | Subtract Magnitudes |                                         |          |  |

|-----------|----------------|---------------------|-----------------------------------------|----------|--|

|           |                | When A>B            | When A <b< th=""><th>When A=B</th></b<> | When A=B |  |

| (+A)+(+B) | +(A+B)         |                     |                                         |          |  |

| (+A)+(-B) |                | +(A-B)              | -(B-A)                                  | +(A-B)   |  |

| (-A)+(+B) |                | -(A-B)              | +(B-A)                                  | +(A-B)   |  |

| (-A)+(-B) | -(A+B)         |                     |                                         |          |  |

| (+A)-(+B) |                | +(A-B)              | -(B-A)                                  | +(A-B)   |  |

| (+A)-(-B) | +(A+B)         |                     |                                         |          |  |

| (-A)-(+B) | -(A+B)         |                     |                                         |          |  |

| (-A)-(-B) |                | -(A-B)              | +(B-A)                                  | +(A-B)   |  |

Table : Addition and Subtraction of Signed Magnitude Numbers

## Subtract Algorithm

- When the signs of A and B are different add the two magnitudes and attach the sign of A to the result.

- When the signs of A and B are identical compare the magnitudes and subtract the smaller number from the larger. Choose the sign of the result to be the same as A if A>B or the complement of the sign of A if A<B.if the two magnitudes are equal subtract b from a and make the sign of the result positive.

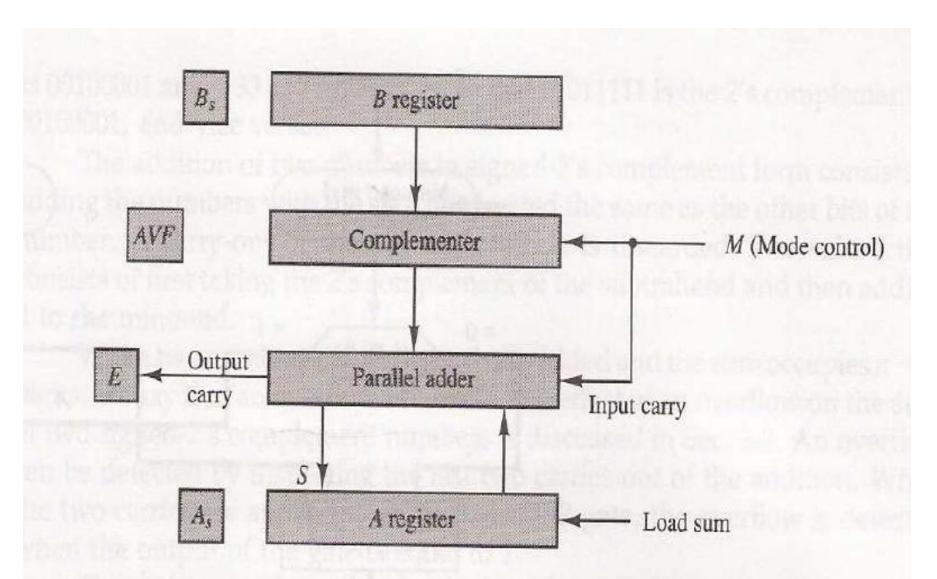

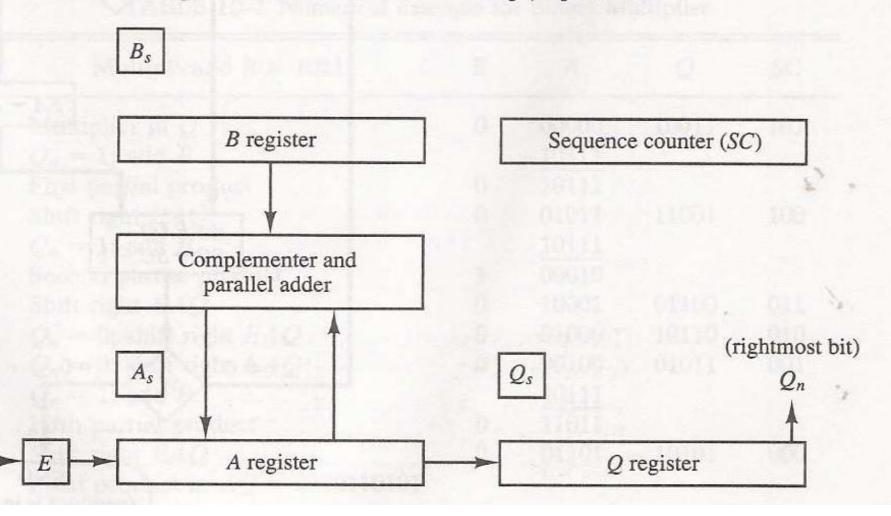

## Addition and Subtraction Hardware Implementation

- We need Two registers to store two numbers and two flip flops to store signs of numbers.

- It requires a parallel adder to perform the micro operation A+B.

- A comparator circuit is needed to compare A>B,A<B,A=B.

- The output carry flag.

- The add over flow flip flop AVF holds the overflow bit when A and B are added.

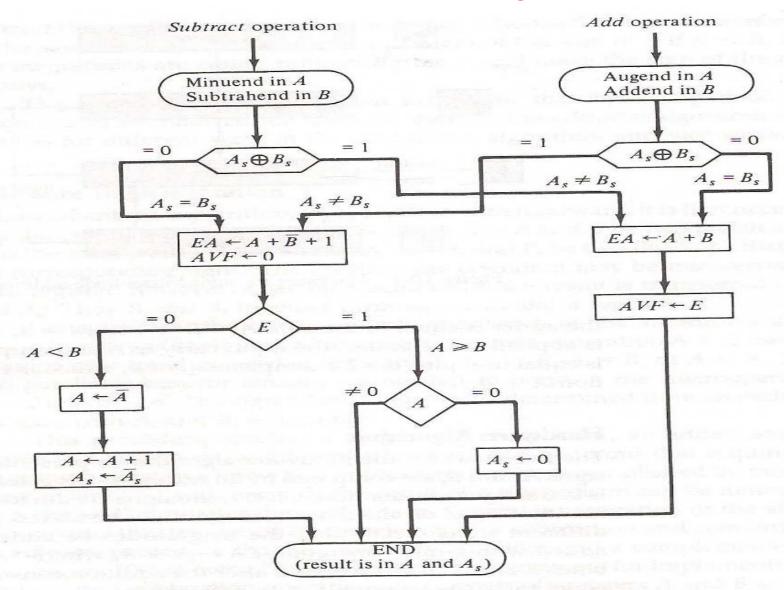

Figure 10-1 Hardware for signed-magnitude addition and subtraction.

#### Addition and Subtract Algorithm

Figure 10-2 Flowchart for add and subtract operations.

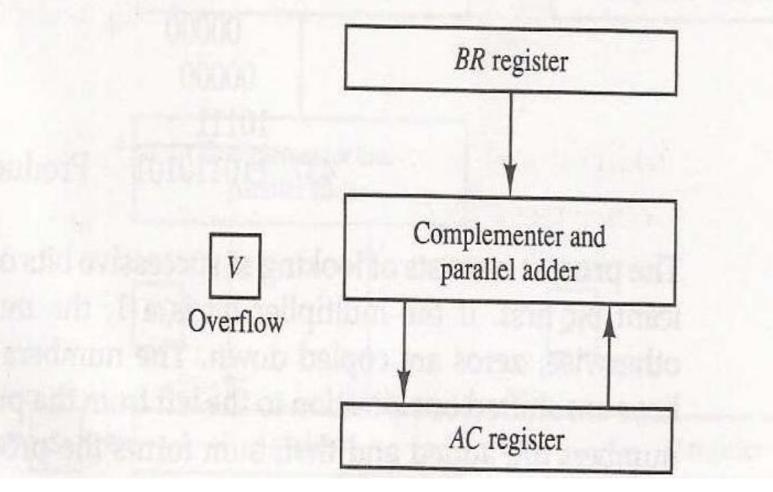

#### Addition and Subtraction with Signed 2's Complement Data

Figure 10-3 Hardware for signed-2's complement addition and subtraction.

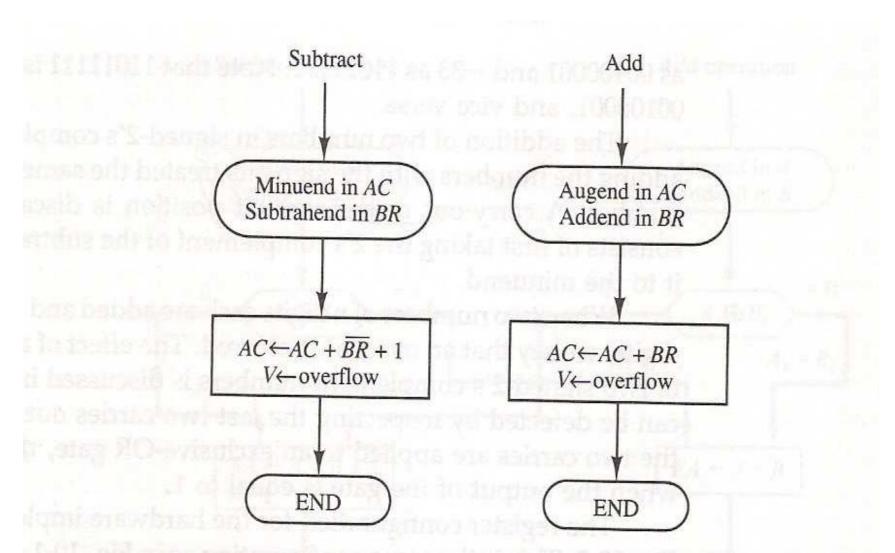

#### Addition and Subtraction with Signed 2's Complement Data

Figure 10-4 Algorithm for adding and subtracting numbers in signed-2's complement representation.

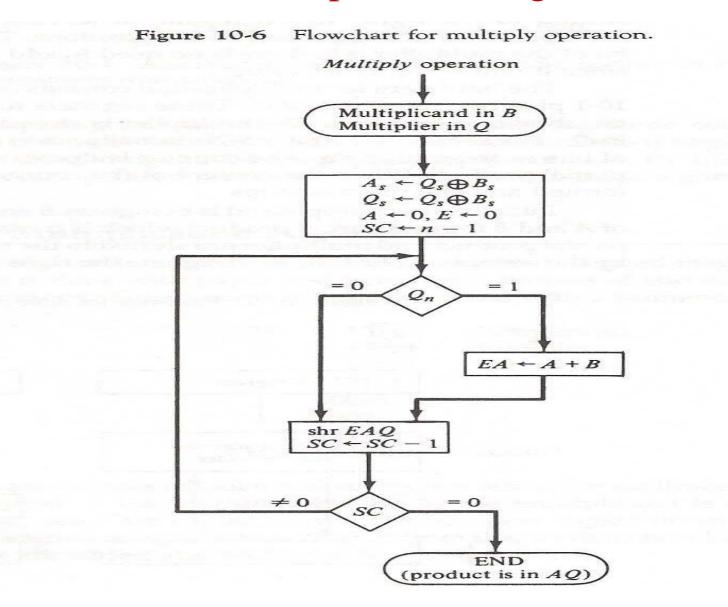

Figure 10-5 Hardware for multiply operation.

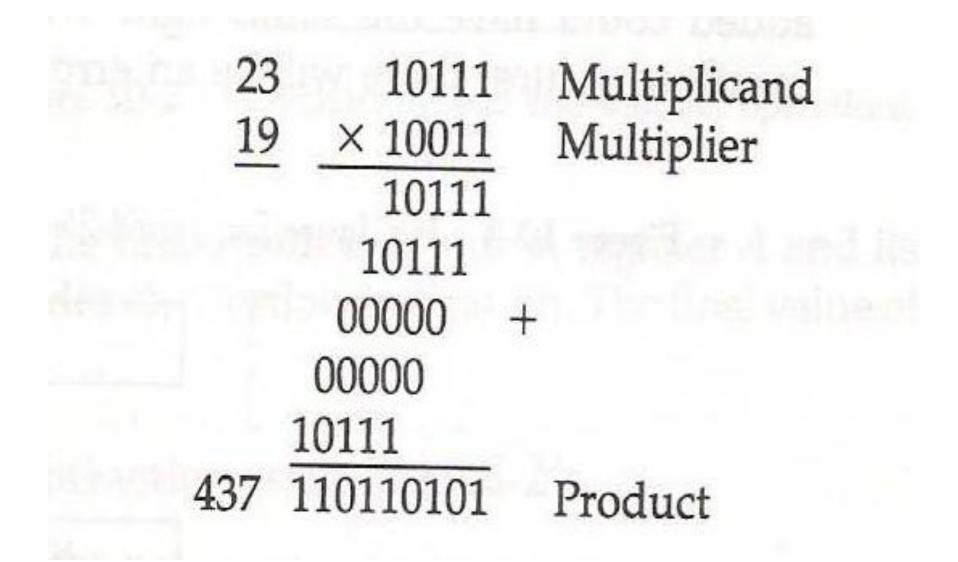

TABLE 10-2 Numerical Example for Binary Multiplier

| Multiplicand $B = 10111$           | E | Α     | Q     | SC    |   |

|------------------------------------|---|-------|-------|-------|---|

| Multiplier in Q                    | 0 | 00000 | 10011 | 101   | - |

| $Q_n = 1$ ; add B                  |   | 10111 |       | 101   |   |

| First partial product              | 0 | 10111 |       |       |   |

| Shift right EAQ                    | 0 | 01011 | 11001 | 100   |   |

| $Q_n = 1$ ; add B                  |   | 10111 |       |       |   |

| Second partial product             | 1 | 00010 |       |       |   |

| Shift right EAQ                    | 0 | 10001 | 01100 | 011   | 1 |

| $Q_n = 0$ ; shift right $EAQ$      | 0 | 01000 | 10110 | 010   |   |

| $Q_n = 0$ ; shift right $EAQ$      | 0 | 00100 | 01011 | 001   |   |

| $Q_n = 1$ ; add B                  |   | 10111 |       | , , , |   |

| Fifth partial product              | 0 | 11011 |       |       |   |

| Shift right EAQ                    | 0 | 01101 | 10101 | 000   |   |

| Final product in $AQ = 0110110102$ | 1 |       |       |       |   |

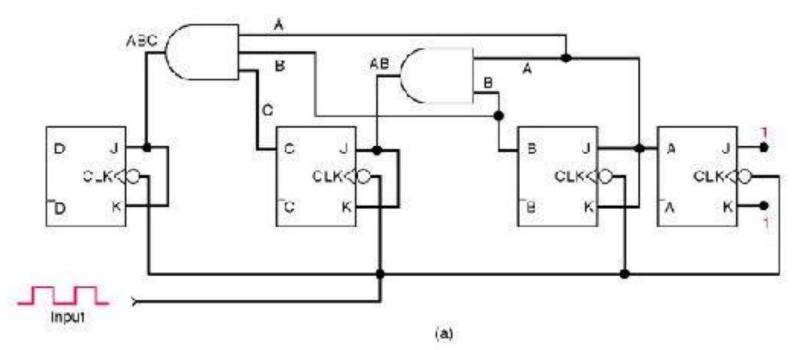

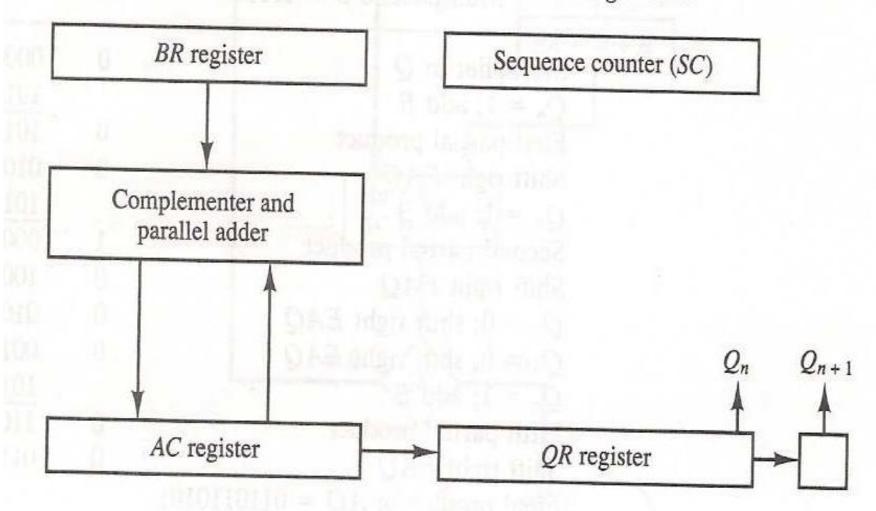

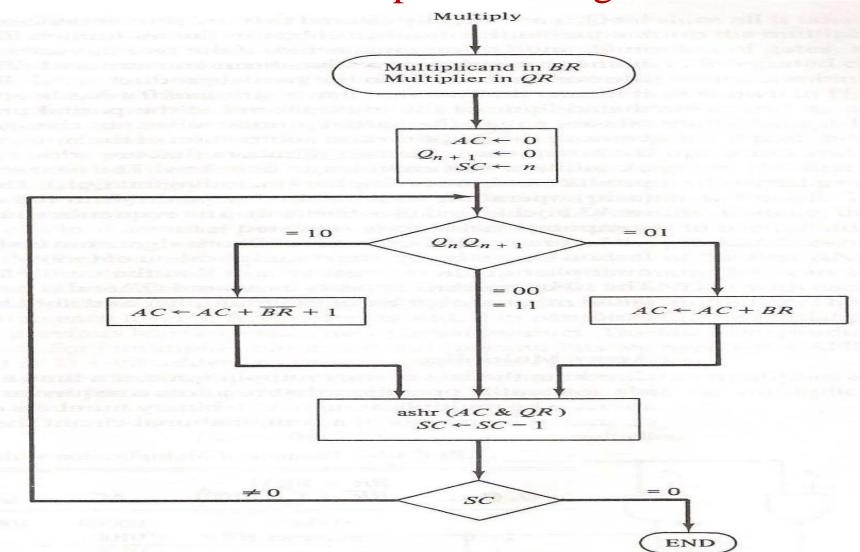

- Booth algorithm gives a procedure for multiplying binary integers in signed 2's complements representation.

- Here it it treats a string of 1's in the multiplier from bit weight  $2^k$  to bit weight  $2^m$  can be treated as  $2^{k+1}-2^{m}$ .

- The binary number 001110 has a string of 1's from  $2^3$  to  $2^1(k=3,m=1)$ .the number can be represented as  $2^{k+1}-2^m=2^4-2^1=16-2=14$ .

- So the product is obtained by M \*14. where m is Multiplicand 14 is Multiplier can be done as M\*2<sup>4</sup>-M\*2<sup>1</sup>.

- I.E by shifting the binary multiplicand four times to the left and subtract M shifted left once.

- Booth algorithm requires examination of the multiplier bits and shifting of partial product.

- Prior to the shifting the multiplicand may be added to the partial product, subtracted from the partial product or left un changed based on the following rules.

- 1)The multiplicand is subtracted from the partial product upon encountering the first least significant bit is 1 in a string of 1's in the multiplier.

- 2)The multiplicand is added to the partial product upon encountering the first 0 in a string of 0's in the multiplier.

- 3) The partial product does not change when the multiplier bit is identical to the previous multiplier bit.

Negative:-14=110010 as -2<sup>4</sup>+2<sup>2</sup>-2<sup>1</sup>.

Figure 10-7 Hardware for Booth algorithm.

Figure 10-8 Booth algorithm for multiplication of signed-2's complement numbers.

Example of Multiplication with Booth Algorithm

| Qn Q | Q <sub>n+1</sub> | $\frac{BR}{BR} = 10111$<br>$\frac{BR}{BR} + 1 = 01001$ | AC    | QR    | <i>Q</i> <sub><i>n</i>+1</sub> | SC   |

|------|------------------|--------------------------------------------------------|-------|-------|--------------------------------|------|

| 1    |                  | Initial                                                | 00000 | 10011 | 0                              | 101  |

| 1    | 0                | Subtract BR                                            | 01001 |       |                                |      |

|      |                  |                                                        | 01001 |       |                                |      |

|      |                  | ashr                                                   | 00100 | 11001 | 1                              | 100  |

| 1    | 1                | ashr                                                   | 00010 | 01100 | 1                              | 011  |

| 0    | 1                | Add BR                                                 | 10111 |       |                                | 1000 |

|      |                  |                                                        | 11001 |       |                                | ,    |

|      |                  | ashr                                                   | 11100 | 10110 | 0                              | 010  |

| 0    | 0                | ashr                                                   | 11110 | 01011 | 0                              | 001  |

| 1    | 0                | Subtract BR                                            | 01001 |       |                                |      |

|      |                  |                                                        | 00111 |       |                                |      |

|      |                  | ashr                                                   | 00011 | 10101 | 1                              | 000  |

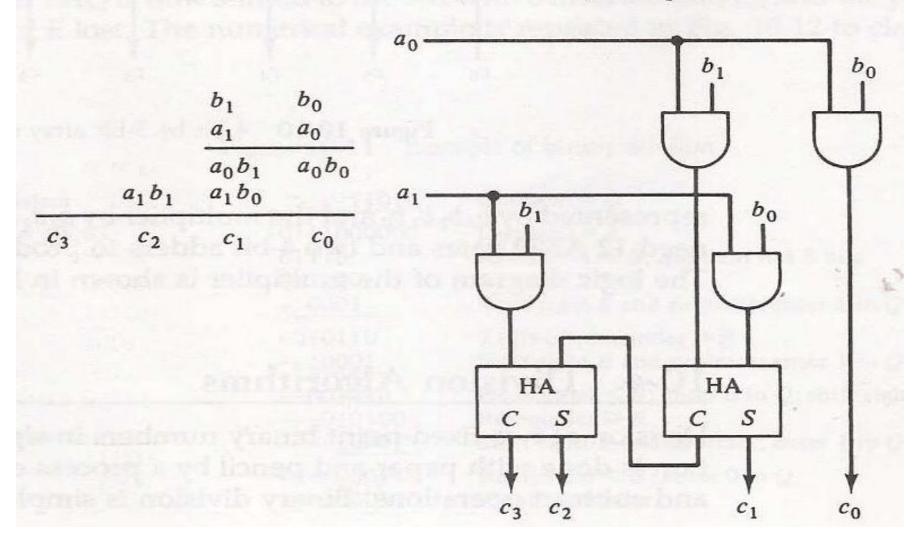

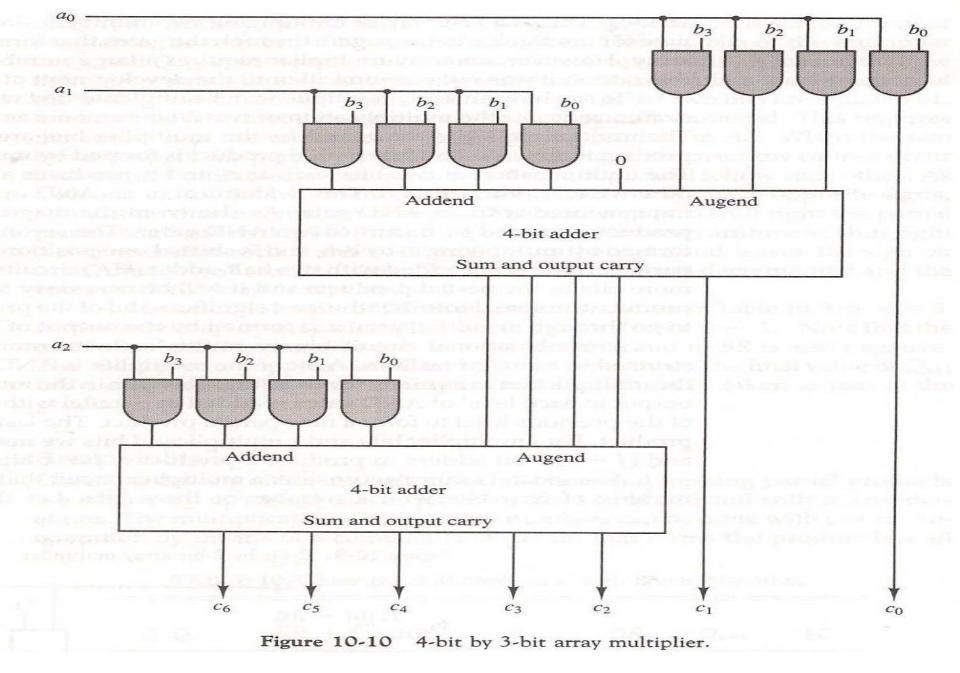

#### Array Multiplier

Figure 10-9 2-bit by 2-bit array multiplier.

## Array Multiplier

#### Array Multiplier

- Example : Multiplicand : 1110 ,Multiplier:111

a0=1,a1=1,a2=1 b0=0,b1=1,b2=1,b3=1

C0=0

| 1 | 0 | 1 | 0 | 1 | c1=1 |

|---|---|---|---|---|------|

| 1 | 1 | 1 | 0 |   |      |

1 1 0 0 0

C0=0,c1=1,c2=0,c3=0,c4=0,c5=1,c6=1

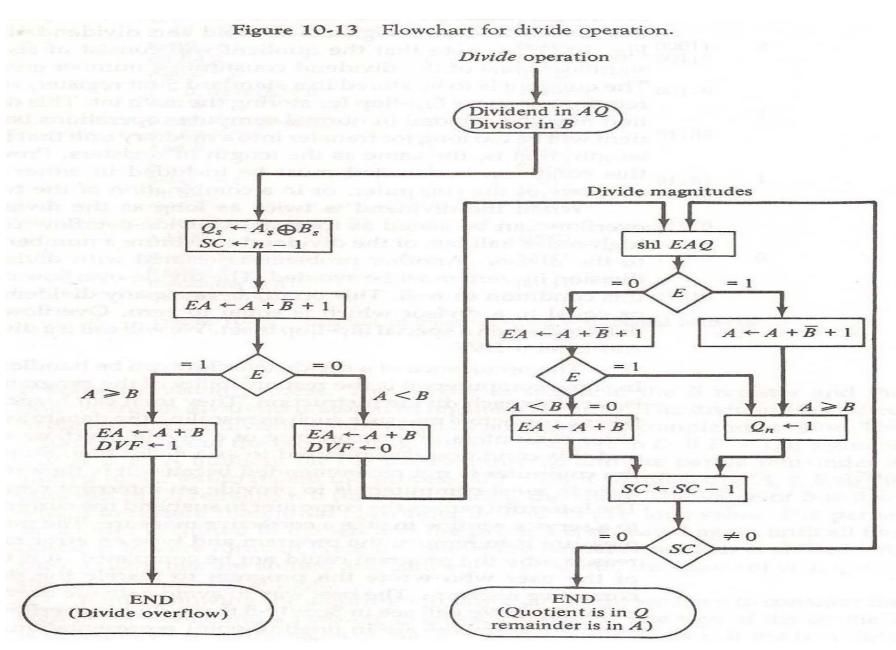

## **Division Algorithm**

Figure 10-11 Example of binary division.

Divisor: B = 10001

11010 /0111000000 01110 011100 -10001 -010110 --10001 --001010 ---010100 ----10001 ----000110 ----00110 Quotient = Q

Dividend = A5 bits of A < B, quotient has 5 bits 6 bits of  $A \ge B$ Shift right B and subtract; enter 1 in Q7 bits of remainder  $\geq B$ Shift right B and subtract; enter 1 in QRemainder < B; enter 0 in Q; shift right B Remainder  $\geq B$ Shift right B and subtract; enter 1 in QRemainder < B; enter 0 in Q Final remainder

| Divisor $B = 100$ | 0 | 1, |

|-------------------|---|----|

|-------------------|---|----|

$\overline{B}$  + 1 = 01111

|                                                               | E           | A                                | Q              | SC |

|---------------------------------------------------------------|-------------|----------------------------------|----------------|----|

| Dividend:<br>shl $EAQ$<br>add $\overline{B}$ + 1              | 0           | 01110<br>11100<br>01111          | 00000          | 5  |

| E = 1<br>Set $Q_n = 1$<br>shl $EAQ$<br>Add $\overline{B} + 1$ | 1<br>1<br>0 | 01011<br>01011<br>10110<br>01111 | 00001<br>00010 | 4  |

| E = 1<br>Set $Q_n = 1$<br>shl $EAQ$<br>Add $\overline{B} + 1$ | 1<br>1<br>0 | 00101<br>00101<br>01010<br>01111 | 00011<br>00110 | 3  |

| $E = 0$ ; leave $Q_n = 0$<br>Add $B$                          | 0           | 11001<br>10001                   | 00110          |    |

| Restore remainder shl $EAQ$<br>Add $\overline{B}$ + 1         | 1<br>0      | 01010<br>10100<br>01111          | 01100          | 2  |

| E = 1<br>Set $Q_n = 1$<br>sh1 $EAQ$<br>Add $\overline{B} + 1$ | 1<br>1<br>0 | 00011<br>00011<br>00110<br>01111 | 01101<br>11010 | 1  |

| $E = 0$ ; leave $Q_n = 0$<br>Add $B$                          | 0           | 10101<br>10001                   | 11010          |    |

| Restore remainder<br>Neglect E                                | 1           | 00110                            | 11010          | 0  |

| Remainder in A :<br>Quotient in Q:                            |             | 00110                            | 11010          |    |

| - Contra starting and starting of the                         |             |                                  |                |    |

Figure 10-12 Example of binary division with digital hardware.

## Divide Overflow

- Conditions for overflow:

- 1)A divide overflow condition occurs if the higher order off bits of the dividend constitute a number grater than or equal to the divisor.

- 2) Division by zero must be Avoided.

• Over flow condition is detected by an special flip flop called divide over flow flip flop(DVF).

## **Division Algorithm**

## **Floating-Point Algorithms**

Figure 10-14 Registers for floating-point arithmetic operations.

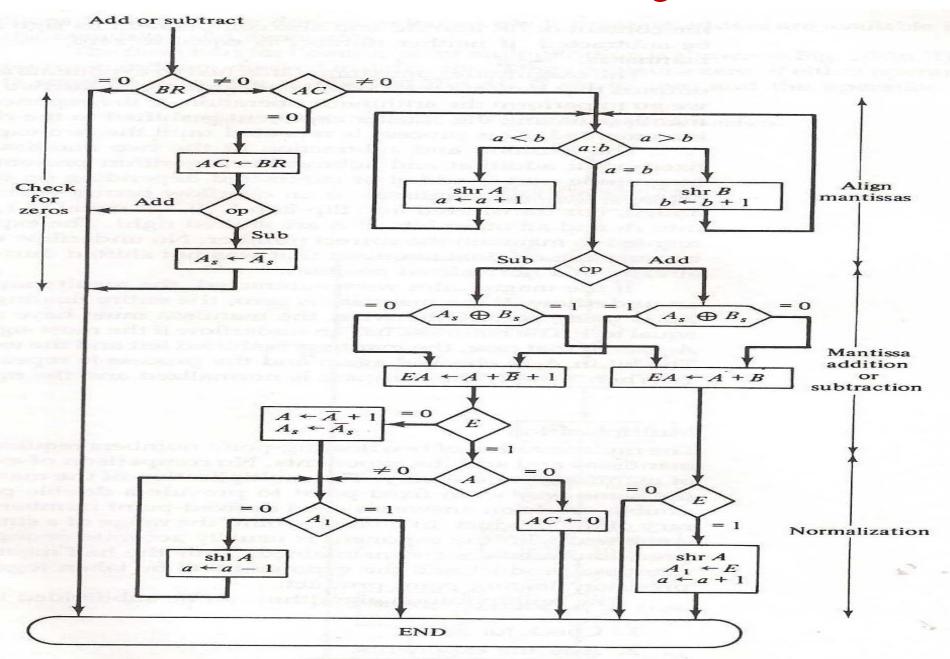

## Addition and Subtraction Algorithm

- 1) Check For Zero.

- 2) Align the Mantissas.

- 3) Add or Subtract the Mantissas.

- 4) Normalize the Result.

#### Addition and Subtraction Algorithm

Figure 10-15 Addition and subtraction of floating-point numbers.

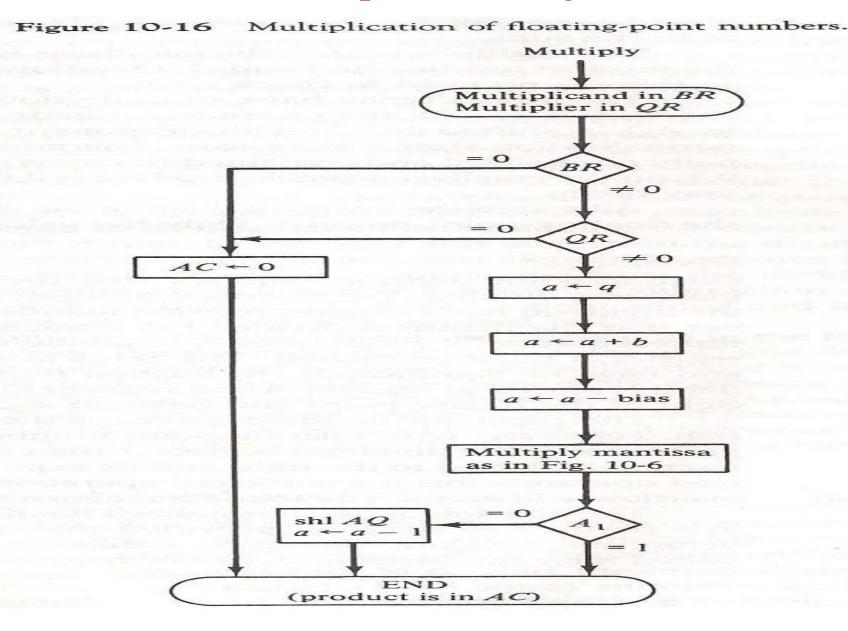

## Multiplication

- 1) Check for Zeros

- 2) Add the Exponents

- 3) Multiply the Mantissas.

- 4) Normalize the Product.

## Multiplication Algorithm

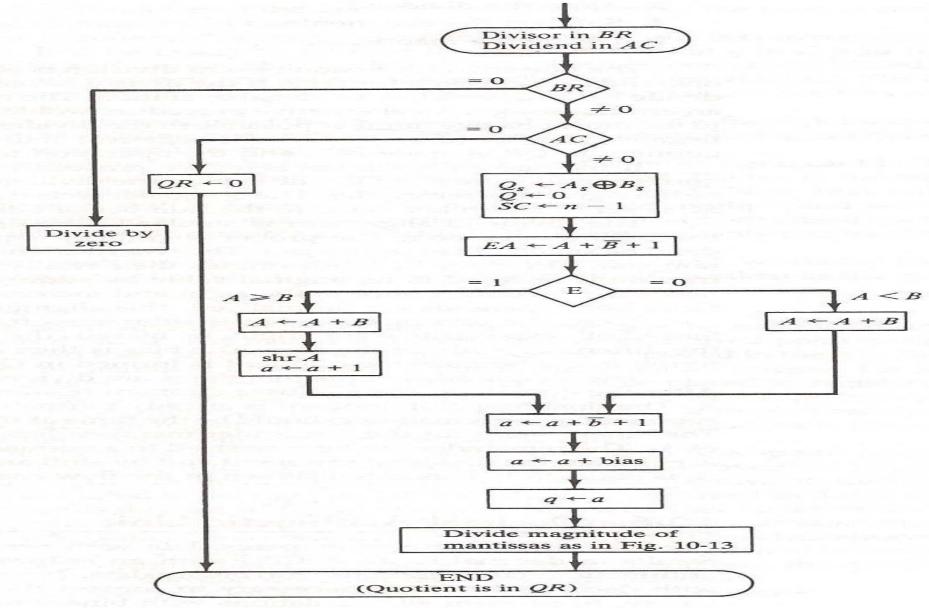

## Division

- 1) Check for Zeros.

- 2) Initialize the register and evaluate the sign.

- 3) Align the dividend.

- 4) Subtract the Exponents.

- 5) Divide the Mantissas.

## **Division Algorithm**

Figure 10-17 Division of floating-point numbers.

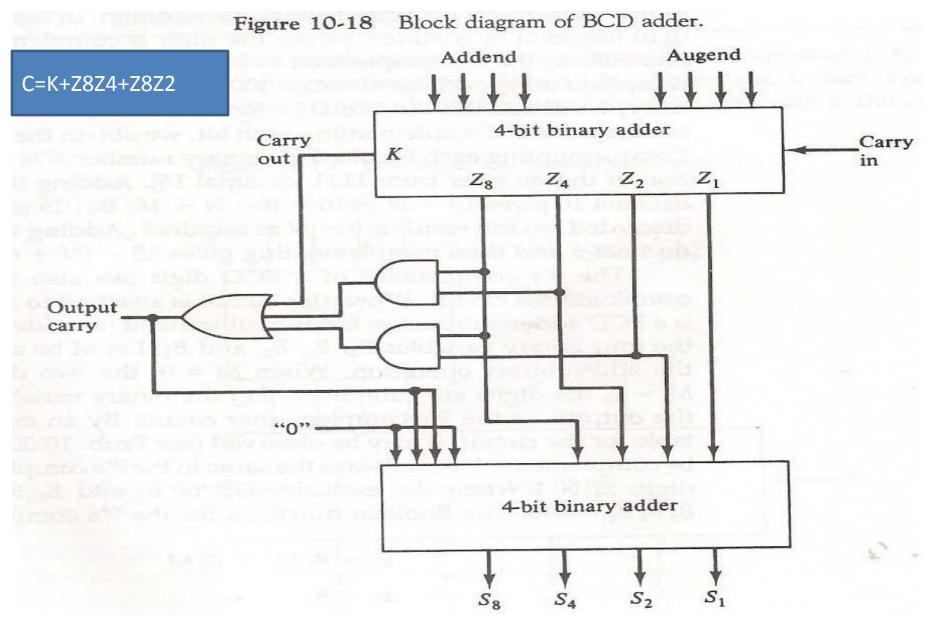

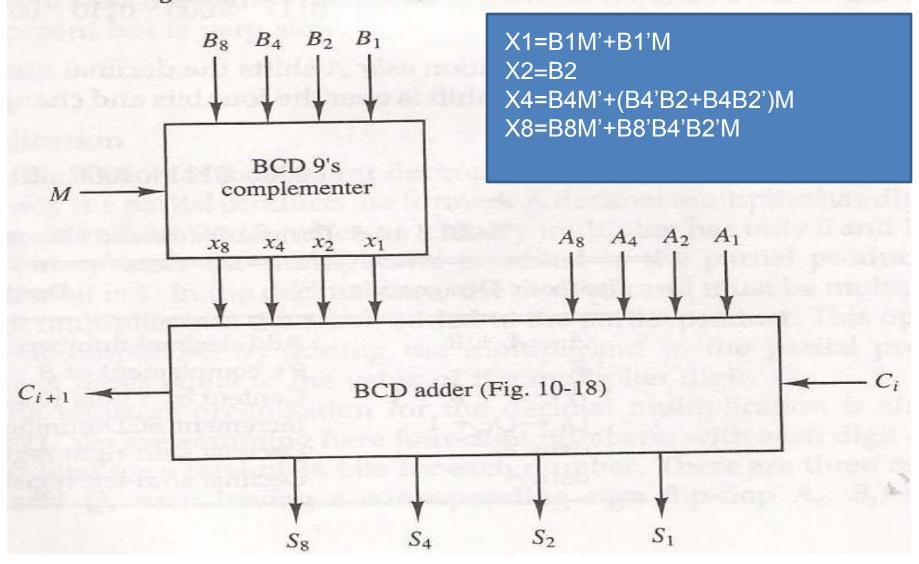

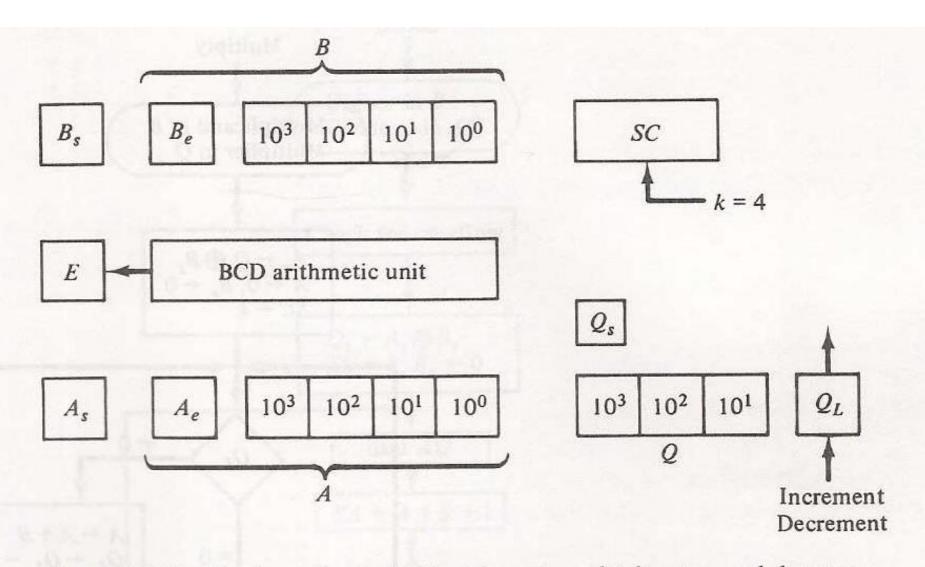

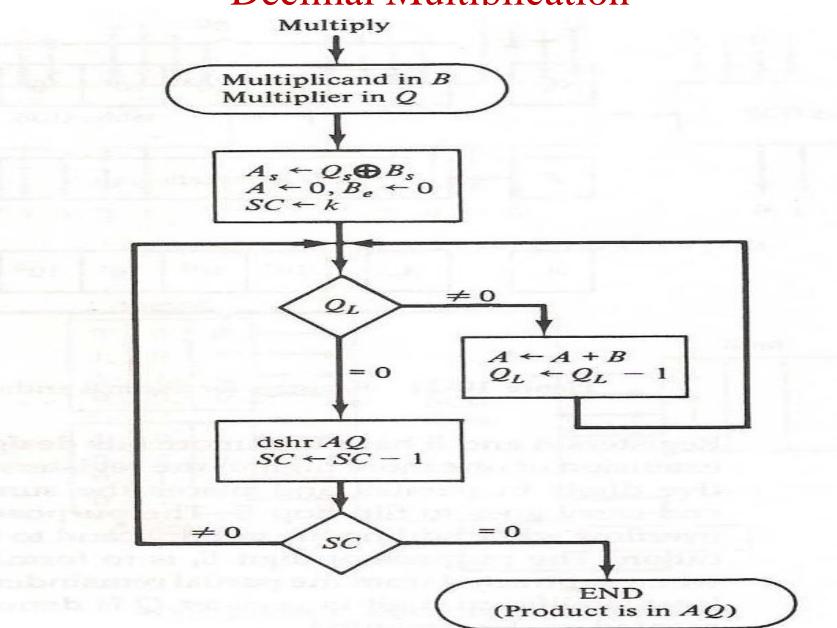

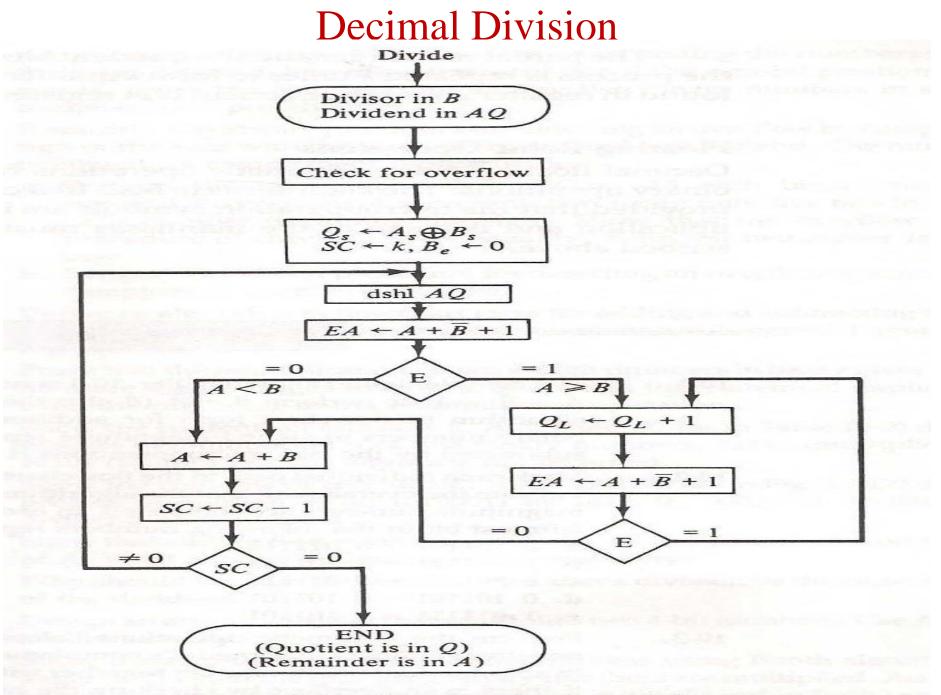

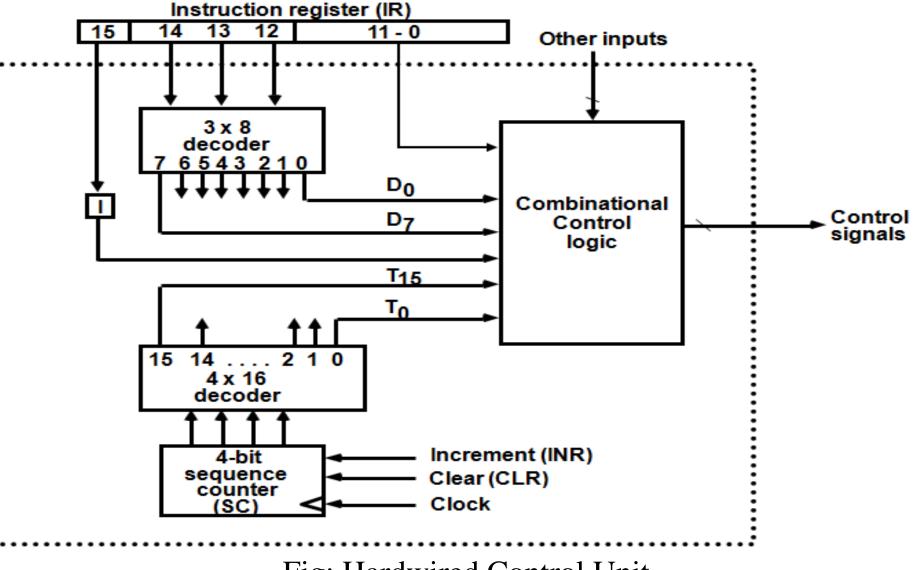

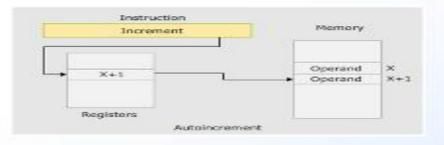

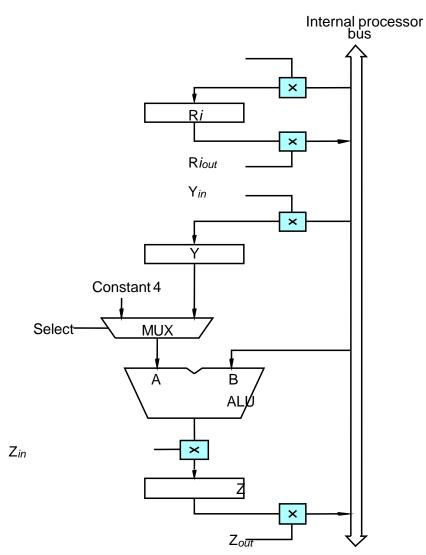

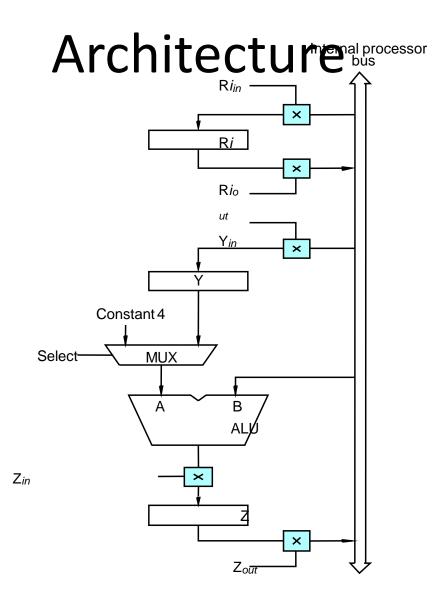

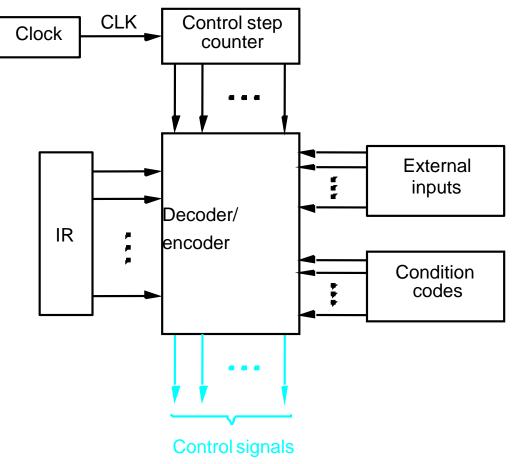

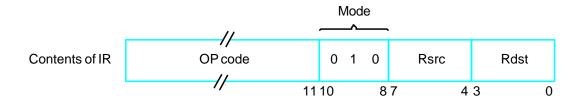

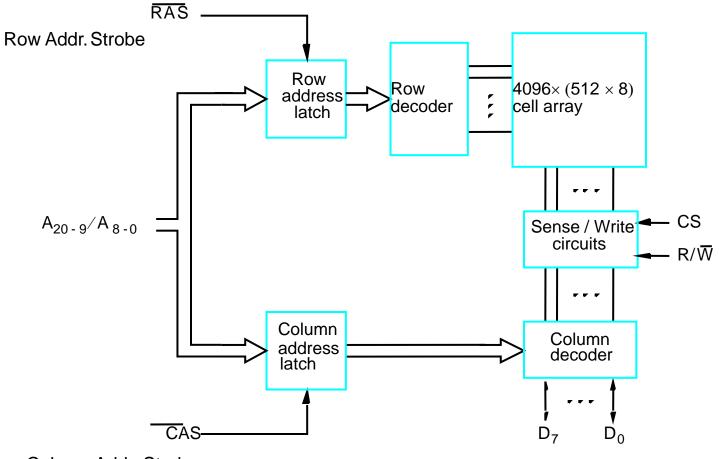

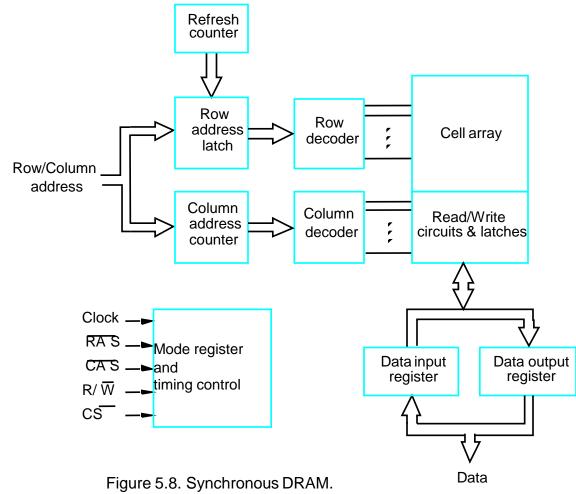

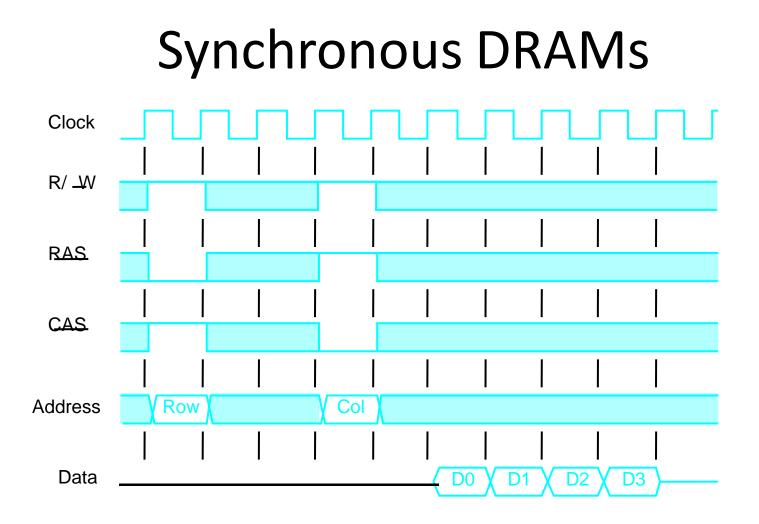

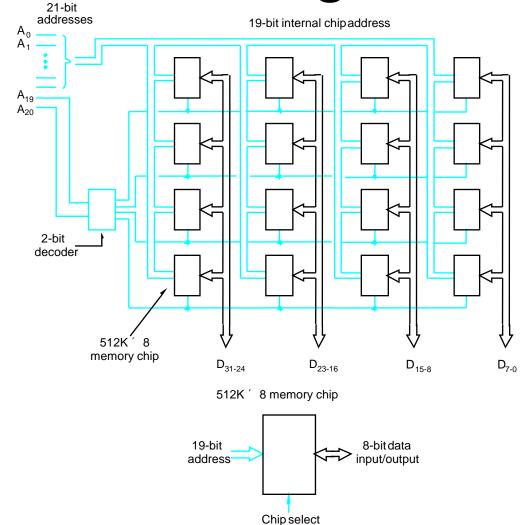

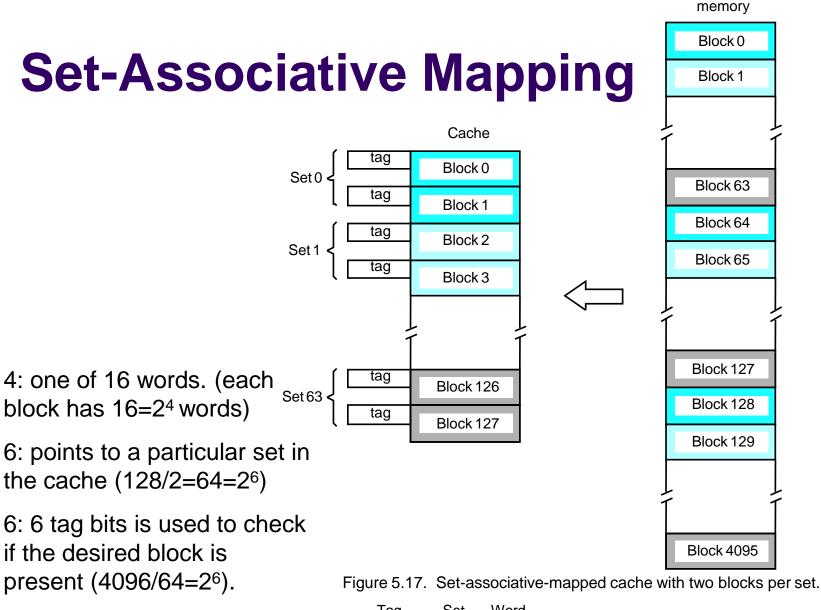

|       | BCD Sum |                |       |                |   | Binary Sum |       |       |                |   |